Parallel Dynamic Voltage and Frequency Scaling for Stream Decoding using a Multicore Embedded System

> Yueh-Min (Ray) Huang National Cheng Kung University

# Outline

- Introduction

- Related work

- System Overview

- Parallel Model

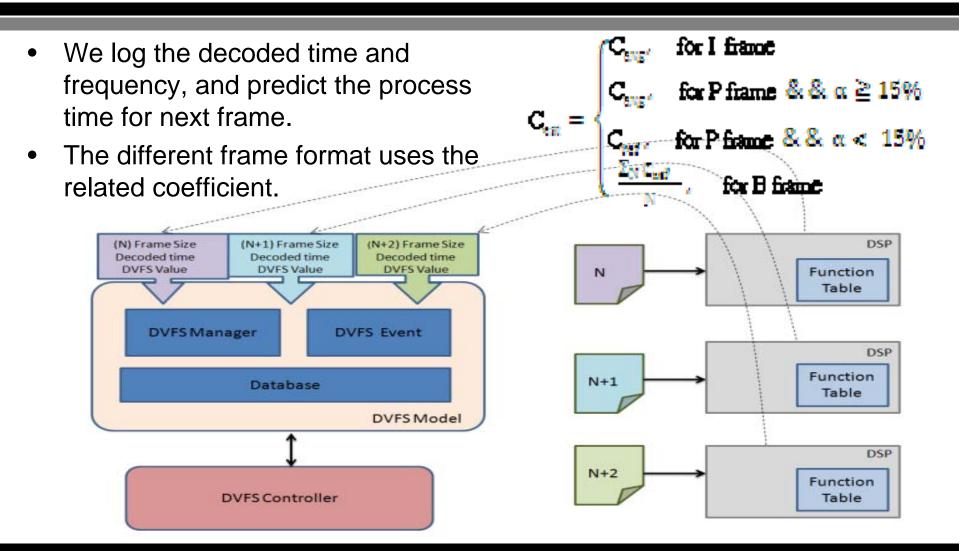

- DVFS Model

- Implement and Result

- Conclusion

## Introduction

- Multicore Embedded System

- With applications needing a more powerful CPU, the newly proposed multi-core designs is a trend for saving power.

- Power Consumption

- Compared to single core platform, multi-core system needs a power managing mechanism to avoid excessive power consumption.

## **Related Work**

- Parallel Computing

- Increase a system processing speed in case of large amount of data or highly complex calculations

- may be grouped into two main types:

- Front-wave parallel processing

- Internal parallel processing.

## **Related Work**

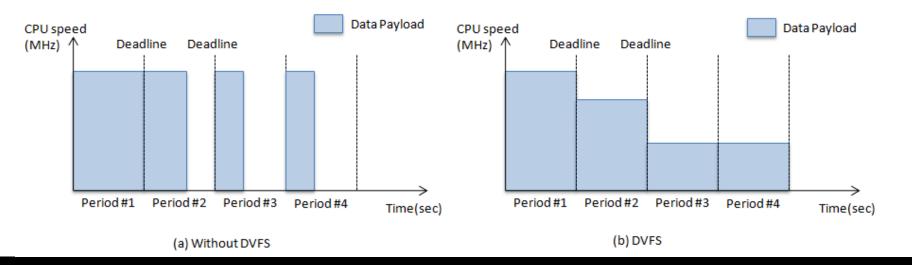

- DVFS: Dynamical Voltage and Frequency Scaling

- Be used to adjust the system voltage or frequency and achieve lower power consumption.

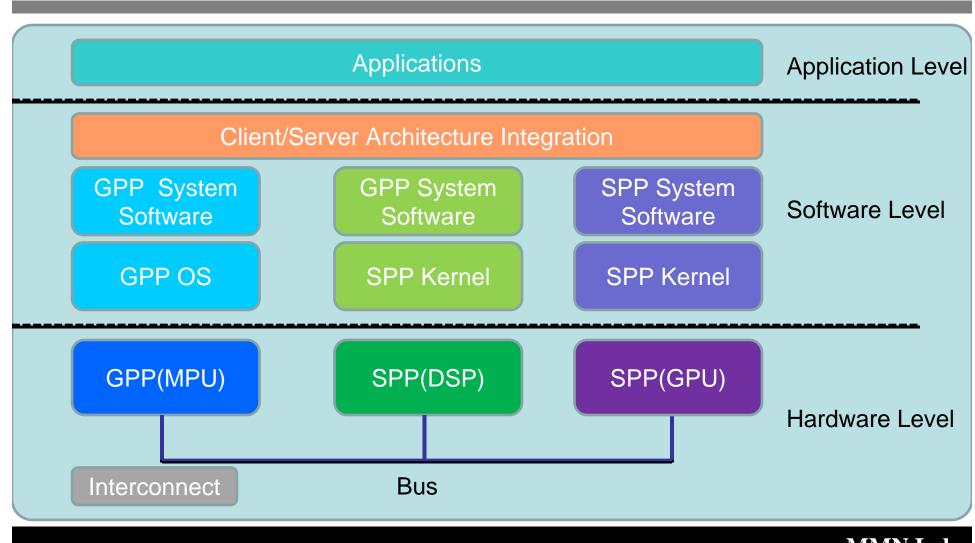

### Common Feature: HMC Architecture Overview

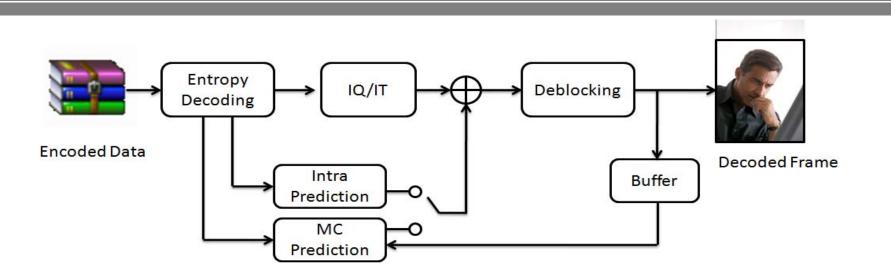

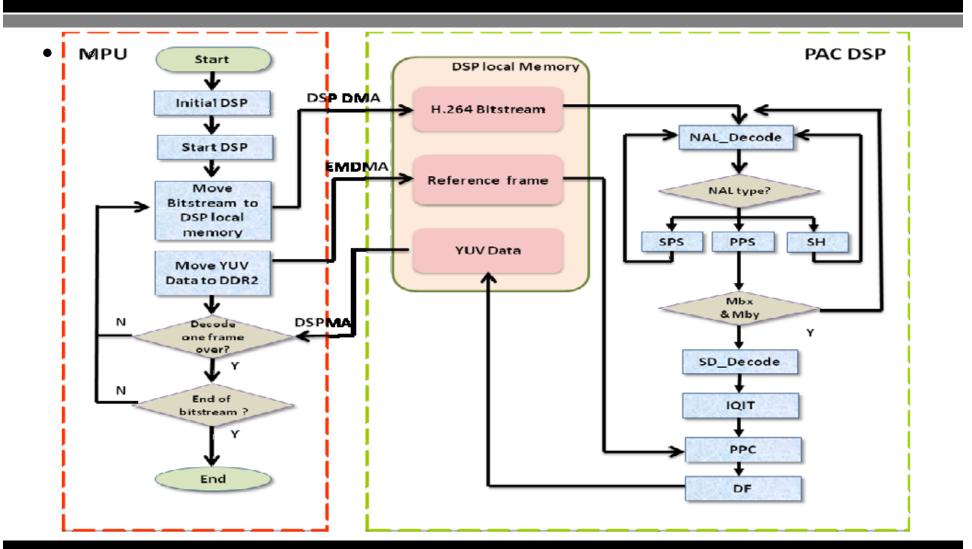

#### Common Feature: H264 Decode Flowchart

- IQ/IT: Inverse Quantization

Inverse Transform

- Intra/Inter Prediction: Spatial domain compression

- Deblocking: Eliminate blocking-effect

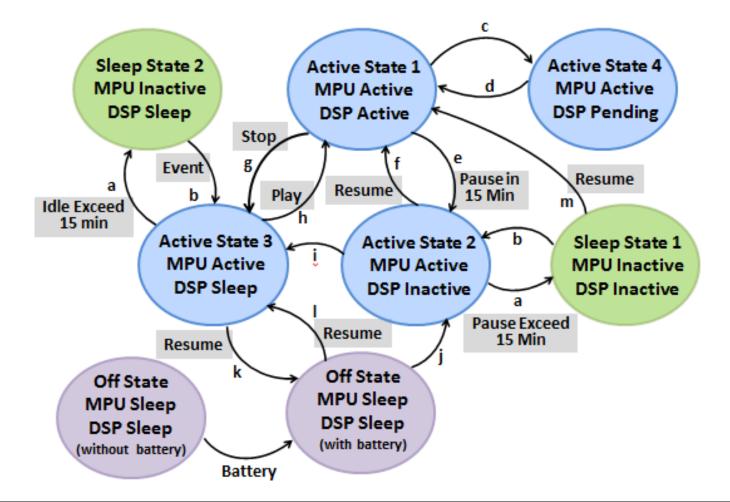

## System Overview

## H.264 Decode on HMC Embedded System

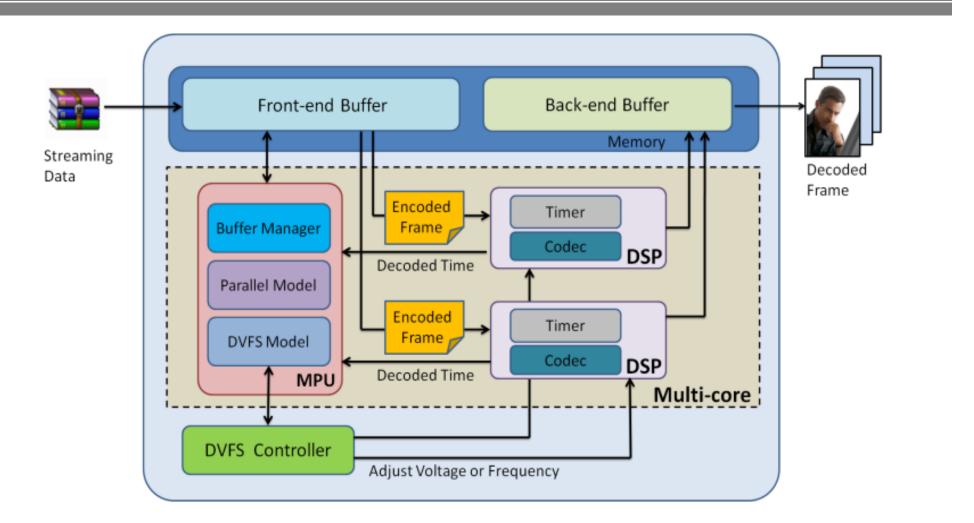

### Parallel Model

The parallel model divided Streaming Data into two parallel ways based on different video format. Front-End Buffer -Data dependent decoding -Data independent decoding  $T = FEB/S + T_{proc} + D$ Parallel Model P2 P3 Ρ4 15 P6 Ρ7 P8 P2 P3 Ρ4 P5 P6 P7 P8 11 11 LSB LSB 15 Ρ2 11 Ρ2 P6 Ρ3 Ρ Ρ4 Ρ3 Ρ7 Ρ5 Ρ P6 P8 Ρ4 P8 Ρ7 Ρ Ρ

## **DVFS** Approach

#### **DVFS Model**

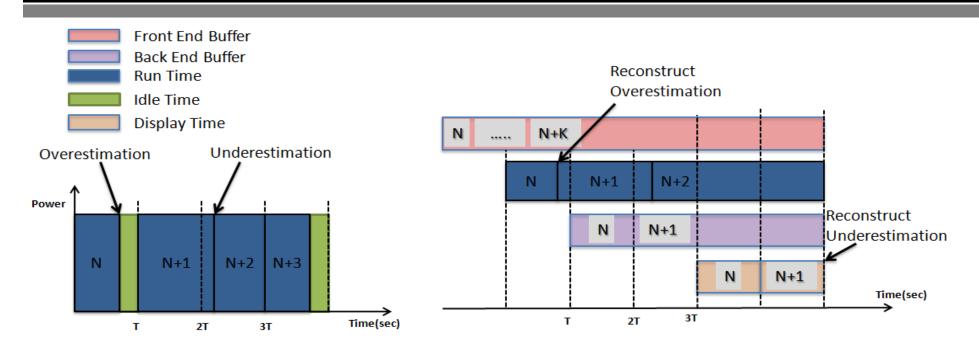

#### **DVFS** Approach with Buffer Mechanism

- Overestimation: Time Slack, Power Loss

- Underestimation: Video frame broken

- FEB: Buffer streaming data, Reconstruct overestimation

- BEB: Buffer decoded data, Reconstruct underestimation

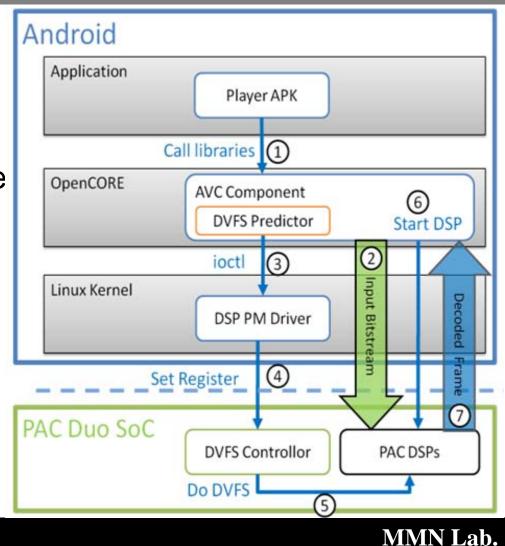

# The Android System Structure and Procedure

- Android 2.2 kernel

- OpenCORE framework

- The DVFS predictor decoder load perform prediction of the appropriate DVFS level.

- Ioctl transfer data to the DSP Power Management Driver and performs DSP voltage and frequency control

## **Power Analysis**

- Platform

- PAC Duo Platform

- Video Format

- H.264 Baseline

Profile(1I29P)

- Power analysis

- FLUKE 8846A

- FLUKEView

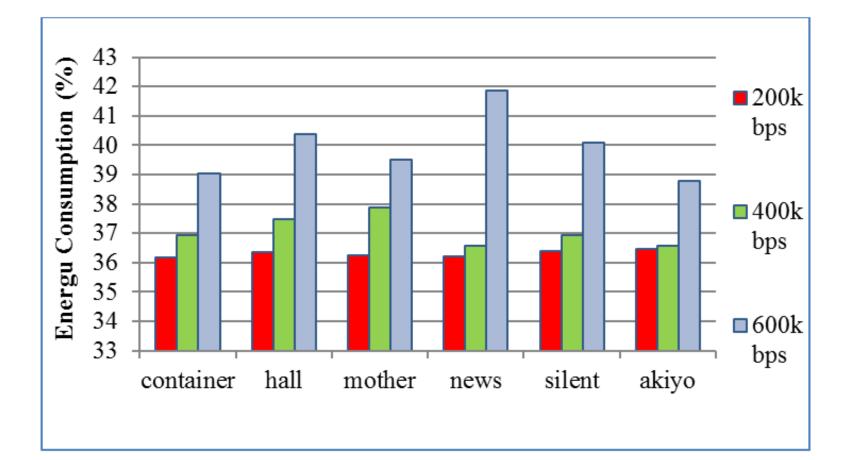

# **Energy Consumption Saving**

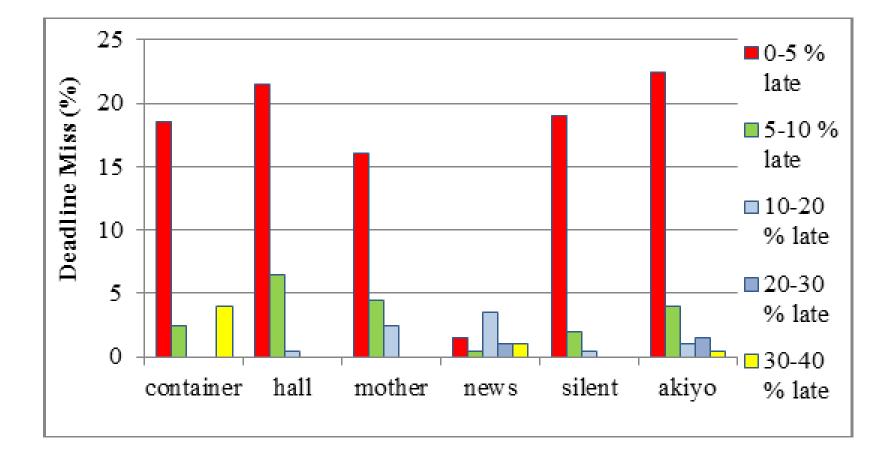

## **Distribution of the Deadline Miss**

## Conclusion

- In this research, we introduced a parallel decoder streaming process for power efficiency perception in a multi-core embedded system by combining multi-core scheduling and a DVFS mechanism to provide a highly efficient and energy multi-media decoding mechanism.

- The experimental results show the decrease of 36.2% to 41.9% in power usage.

## REFERENCES

T. Olivares, F. J. Quiles, P. Cuenca, L. Orozco-Barbosa, and I. Ahmad, "Study of data distribution techniques for the implementation of an MPEG-2 video encoder," *Parallel and Distributed Computing Systems '99*, MIT, Boston, MA, USA, pp. 537–542, Nov. 1999.

D. Farin, N. Mache, and H. N. Peter, "SAMPEG, a scene adaptive parallel MPEG-2 software encoder," *SPIE Visual Communications and Image Processing*, pp. 272–283, Jan. 2001.

M. Flierl and B. Girod, "Generalized B pictures and the draft H. 264/AVC video-compression standard," *IEEE Trans. on Circuits and Systems for Video Technology*, vol. 13, no. 7, pp. 587–597, Jul. 2003.

[4] K. Asanovic, K. Keutzer, D. A. Patterson, et al., "The landscape of parallel computing research: a view from Berkeley," *Tech. Rep. UCB/EECS-2006-183, EECS Department*, University of California, Berkeley, Dec. 2006.

[5] C. Jike, N. Satish, B. Catanzaro, K. Ravindran, and K. Keutzer, "Efficient parallelization of H.264 decoding with macro block level scheduling," *IEEE International Conference on Multimedia and Expo*, pp.1874–1877, July 2007.

[6] A. Azevedo, C. Meenderinck, B. Juurlink, A. Terechko, J. Hoogerbrugge, M. Alvarez, and A. Rammirez, "Parallel H.264 decoding on an embedded multicore processor," in *Proc. 4th International Conference on High Performance and Embedded Architectures and Compilers, HiPEAC*, Paphos, Cyprus, pp. 404–418, Jan. 2009.

## REFERENCES

[7] E. van der Tol, E. Jaspers, and R. Gelderblom, "Mapping of H.264 decoding on a multiprocessor architecture," *Image and Video Communications and Processing 2003*, pp. 707–718, May 2003.

[8] S. Yaldiz, A. Demir, and S. Tasiran, "Stochastic modeling and optimization for energy management in multicore systems: a video decoding case study," *IEEE Trans. on CAD of Integrated Circuits and Systems*, vol. 27, pp. 1264–1277, July 2008.

[9] P. Francesco, P. Antonio, B. Davide, B. Luca, and M. Poletc, "Energy-efficient multiprocessor systems-on-chip for embedded computing: exploring programming models and their architectural support," *IEEE Trans. on Computers*, vol. 56, pp. 606–621, May 2007.

[10] S. Lee, "Low-power video decoding on variable voltage processor for mobile multimedia applications," *ETRI Journal*, vol. 27, pp. 504–510, Oct. 2005.

[11] E. Nurvitadhi, B. Lee, C. Yu, and M. Kim, "A comparative study of dynamic voltage scaling techniques for low-power video decoding," *International Conference on Embedded Systems and Applications*, pp. 23–26, June 2003.