#### **Green Chips**

in particular

Vancouver, November 12-13, 2013

2 ALLANDA

# Optimization is the Keyword in NanoCMOs

Ricardo Reis

# Where do we come from ...

¥2

#### Where do we come from

### Porto Alegre

## Porto Alegre

1111 1111

Thereasting Inconstruction

mmmmm

111111

XXX

$\Pi$

$\mathbb{H}$

#### Ibere Camargo Museum

#### Porto Alegre

#### Instituto de Informática

## CEITEC

Design Center - Administrative Building: Design Center Process Engineering Adm. Offices Teaching Rooms Auditorium 5.100 m<sup>2</sup> **Manufacturing Building**

Manufacturing Cleanroom Research & Development Cleanroom Facilities and Support 9.600 m<sup>2</sup>

4.000 wafers/month (200 a 15.000 chips/ wafers)

# CEITEC

### A bit of History

1984 – Access to MPW prototyping (fabricated at ES2, France)

1986 – RISCO 16b/32b completed First RISC Microprocessor in Brazil (Architecture to Layout)

#### 2012

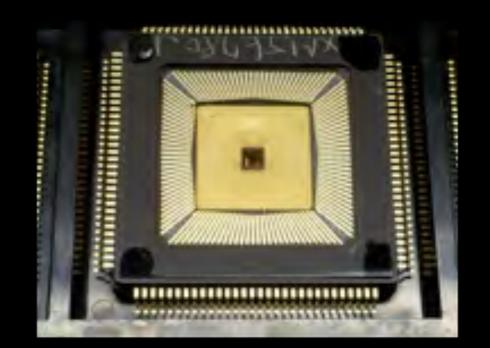

## TMR MIPS Duo Core 32 bits chip tolerant radiation effects

see more at: <a href="http://www.nscad.org.br/site/nsc21101">http://www.nscad.org.br/site/nsc21101</a>

Microelectronics Group Research Topics Embedded Systems Analog Design Digital Design Design Methodologies VLSI Architectures and Dedicated Architectures Digital TV

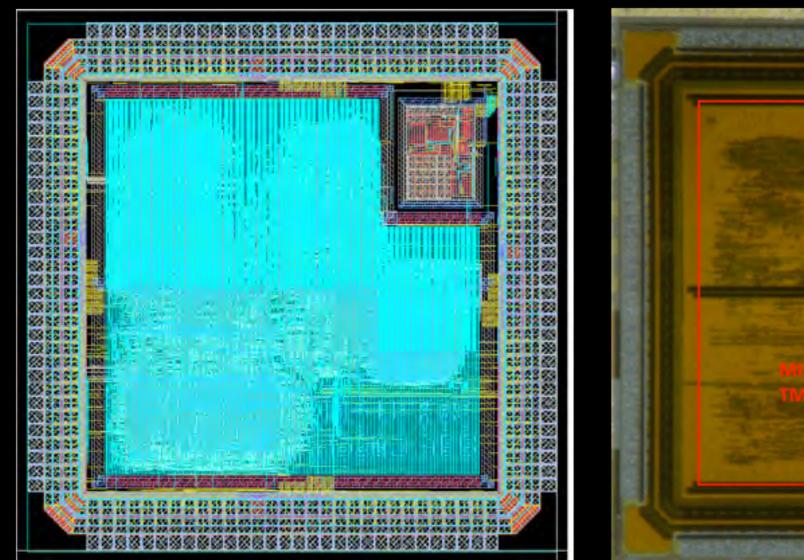

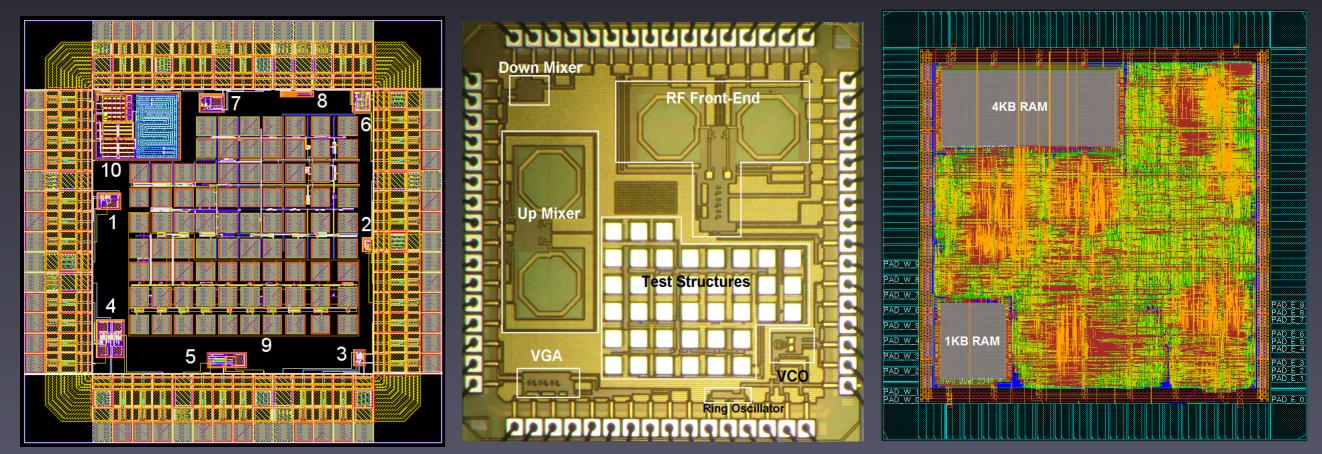

A Multi-Band RF Front End interface

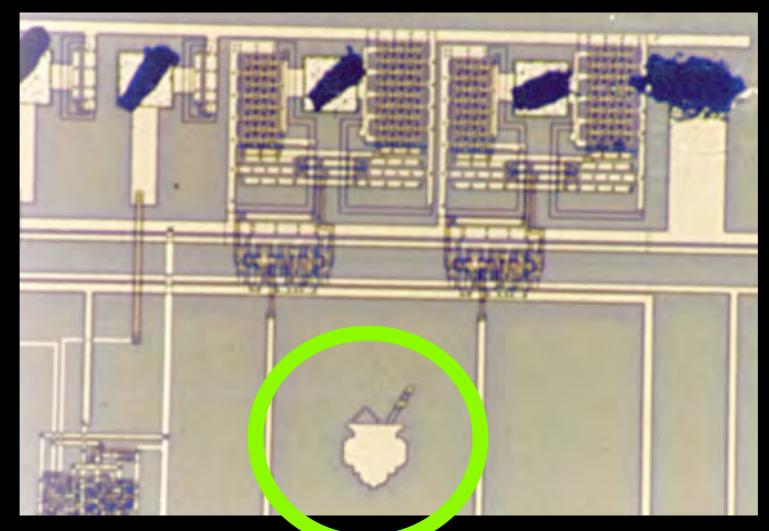

A block of the video decoder

#### **Microelectronics Group Research Topics**

- SoC Systems on a Chip

- **NoC Networks on Chip**

- MEMs

- DSP Systems (video, voice, image) FPGA Design Methodologies

ASIC - CA-VL Coding module CABAC coder/decoder - Parser

FPGA H.264 Coder prototyping

Microelectronics Group Research Topics Fault Tolerant Circuits Circuits Tolerant to Radiation Effects Variability

Test

**Mixed Signal**

Electrical testing of RFID 915MHz (CEITEC Design)

65nm CMOS Variability test structures

#### **Microelectronics Group Research Topics**

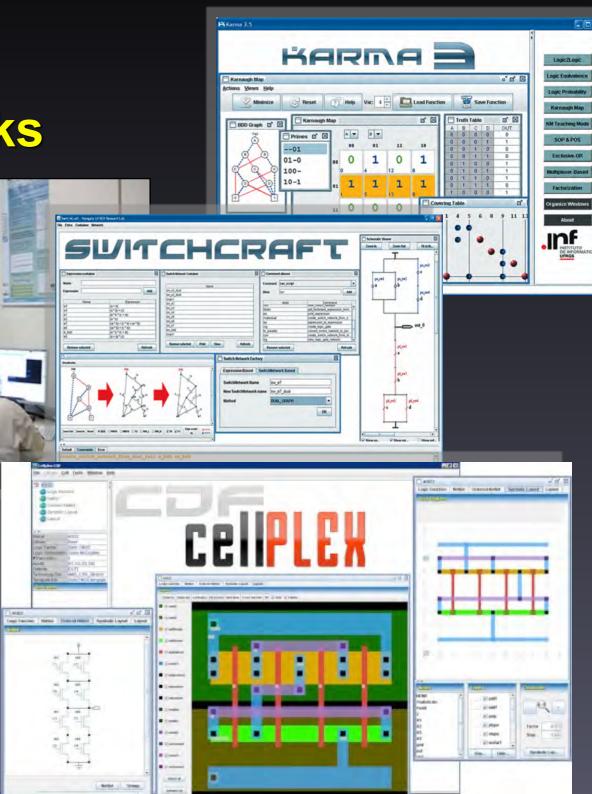

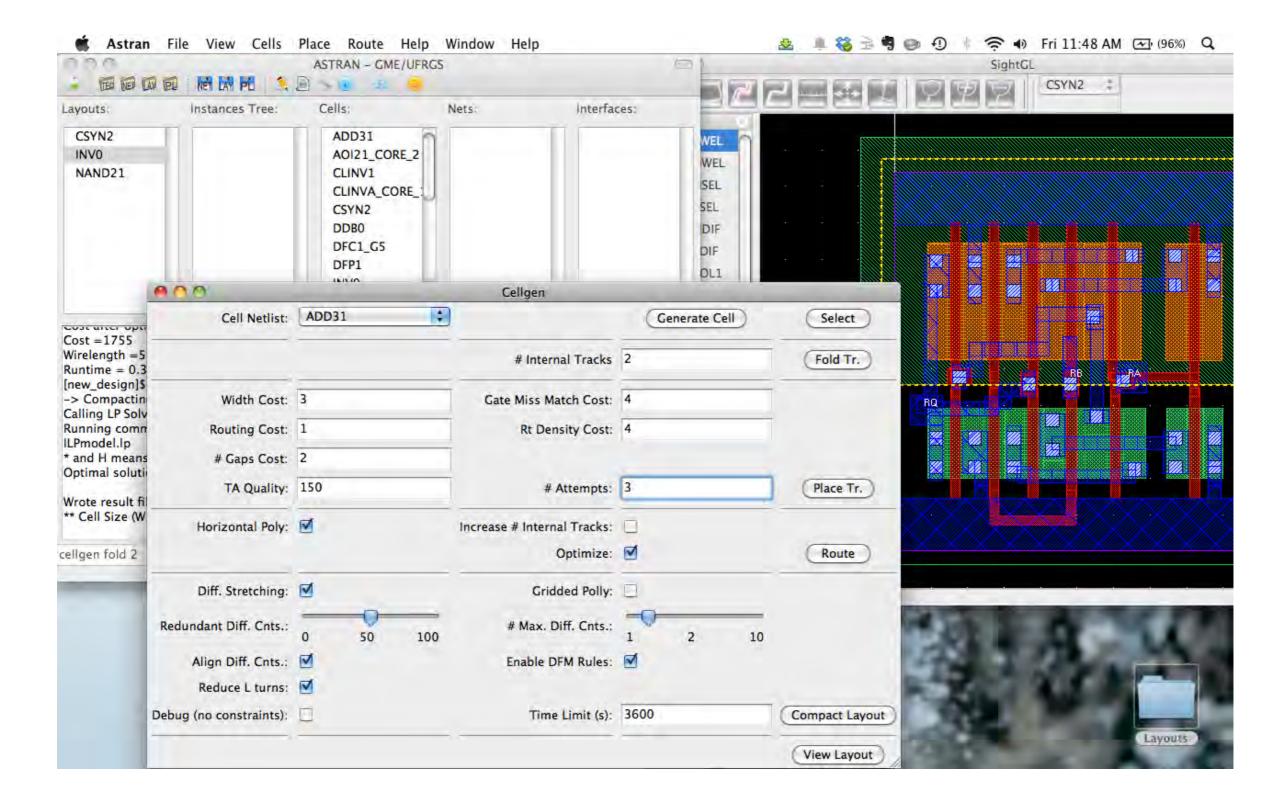

Logic Synthesis Physical Design Design of Transistor Networks EDA Tools

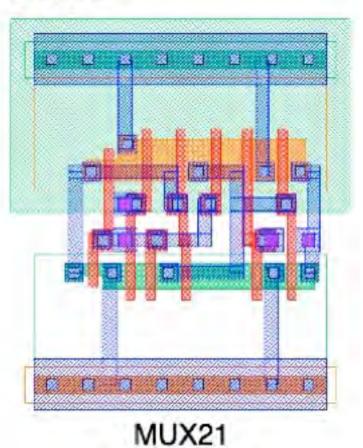

Designed Automatically with ASTRAN

#### **Optimization is the Keyword in NanoCMOs by Ricardo Reis**

Introduction

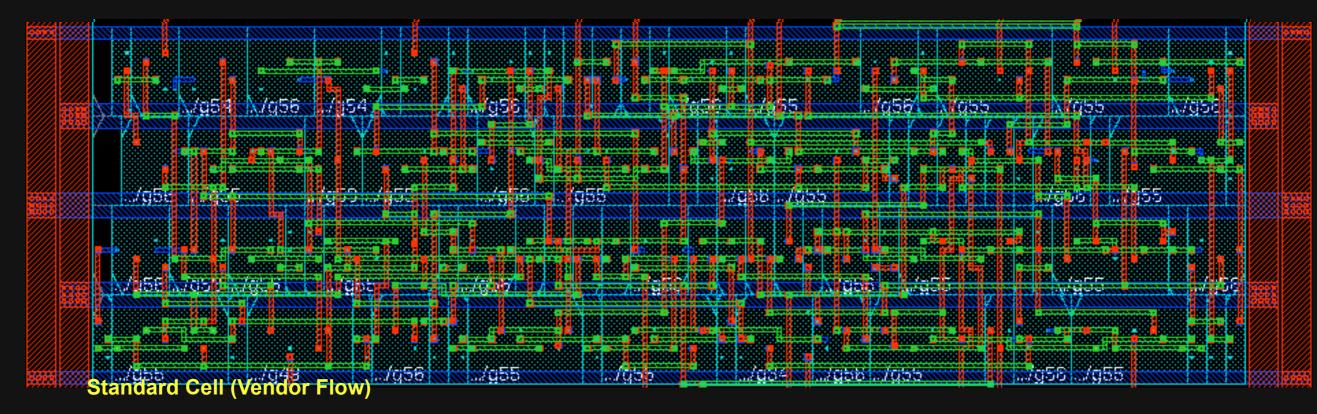

Standard Cell

Power Reduction by using CMOS Complex Gates

Automatic Layout Synthesis

Experimental Results

Conclusions

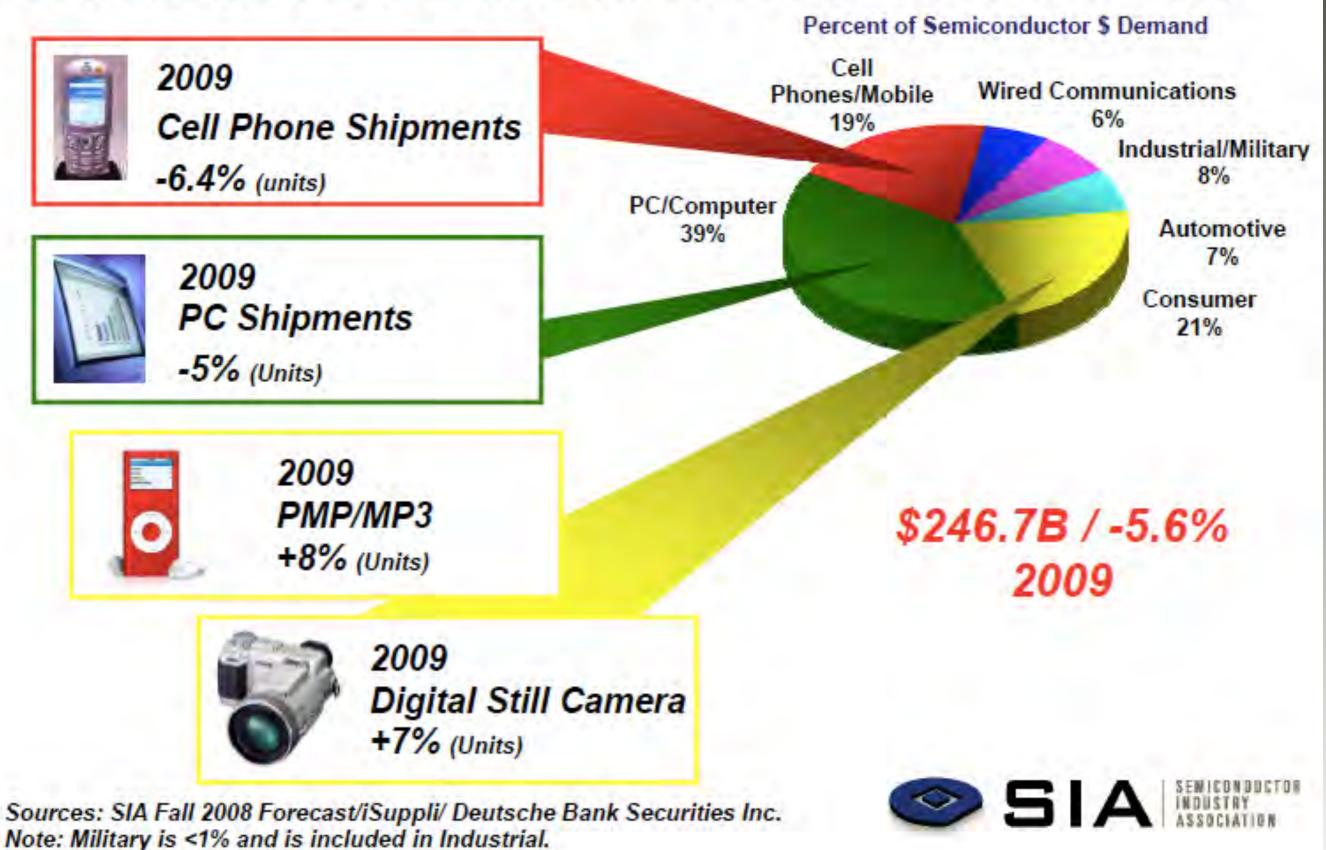

#### Semiconductor Demand Drivers: 2009 Outlook

## 2 Main Problems in NanoCMOS

#### VARIABILITY

POWER (mainly Static Power)

### VARIABILITY

VARIABILITY

VARIABILITYVARIABILITY VARIABILITY VARIABILITY VARIABILITYVARIABILITY VARIABILITY VARIABILITY VARIABILITYVARIABILITY VARIABILITY VARIABILITY VARIABILITYVARIABILITY VARIABILITY VARIABILITY

VARIABILITYVARIABILITYVARIABILITYVARIABILITYVARIABILITYVARIABILITYVARIABILITYVARIABILITYVARIABILITYVARIABILITY VARIABILITY VARIABILITY

VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY VARIABILITY

## VARIABILITY 60 VARIABILITY 56 4 points

VARIABILITY 12 VARIABILITY 8

## Sources/Types of Variability

## Fabrication Technology

### Environment

# Why Optimization is a Keyword in NanoCMOS?

More em More Embedded Systems that requires Low Power

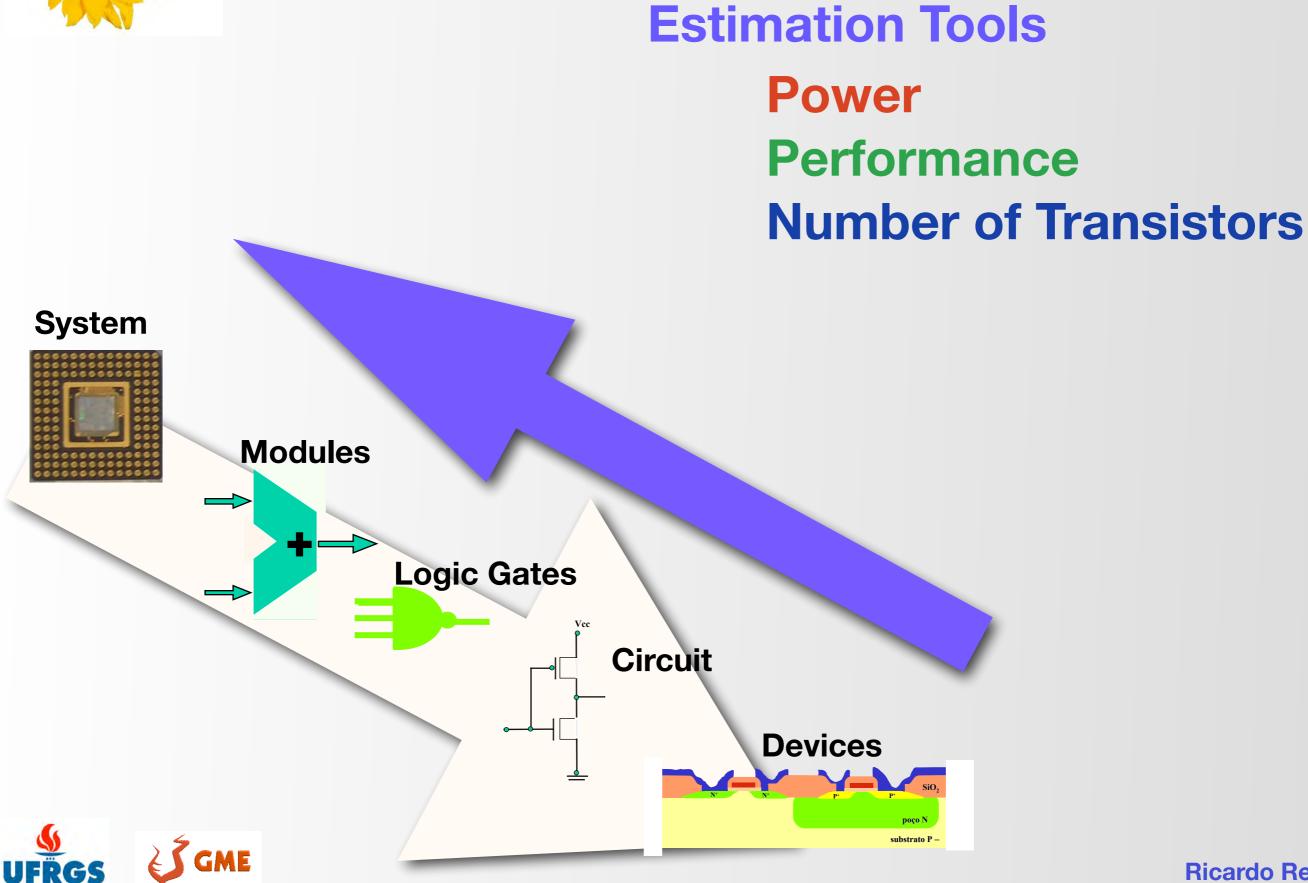

#### **Design Levels of Abstraction**

**Ricardo Reis**

## Power Reduction at Physical Level

## Gate Sizing

# Reduction on the amount of transistors

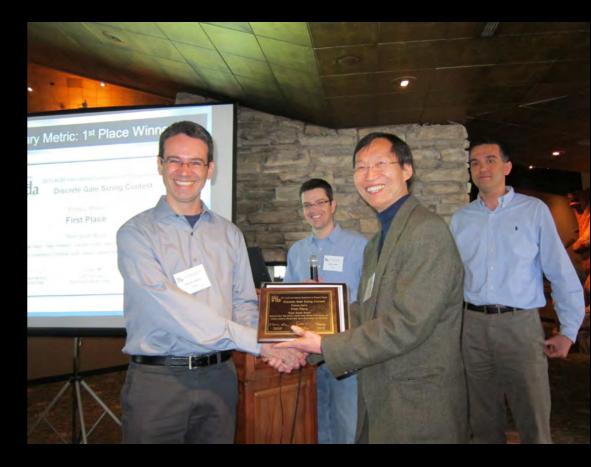

ISPD - International Symposium on Physical Design Discrete Gate Sizing Contest 2012 and 2013

#### organized by Intel

Tiago Reimann, Guilherme Flach, Gracieli Posser Jozeanne Belomo, Marcelo Johann, Ricardo Reis

#### A grain of rice has the price of more than a 100 thousand transistors

Source: The Economist, September 6, 2010

A transistor is cheap BUT Energy is expensive

## Power Consumption drives MOS evolution

NMOS

# Challenge: **Power Optimization** must be done in all levels of abstraction

#### Power Estimation Tools for each level of abstraction

# Power Reduction

leakage is become more and more important in nanocircuits

It is function of the number of transistors

## LESS TRANSISTORS MEANS LESS

## LEAKAGE POWER

# Standard Cell Approach

Cell characterization Cell performance predictability But nowadays cell predictability is not anymore sufficient to have circuit predictability

## Connections becomes a central problem !

## Standard Cell Approach

- Logic Options Limited to Cells Available in the Library

- No optimal logic minimization

- Cells oversized

### Standard Cell Approach

### Far from Minimization on:

- Area

- Number of Transistors

- Wirelenght

- Delay

- Power

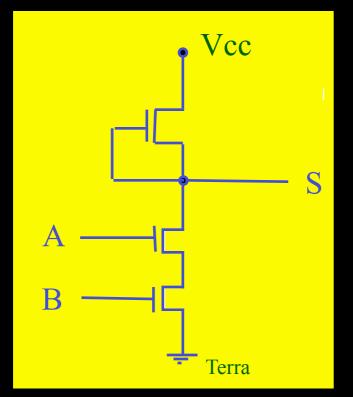

End Years 70: Random Logic Z8000

Years 90: ROMs, PLAs

Next Step: Standard Cell

**Standard Cell 486, Pentium**

M68000

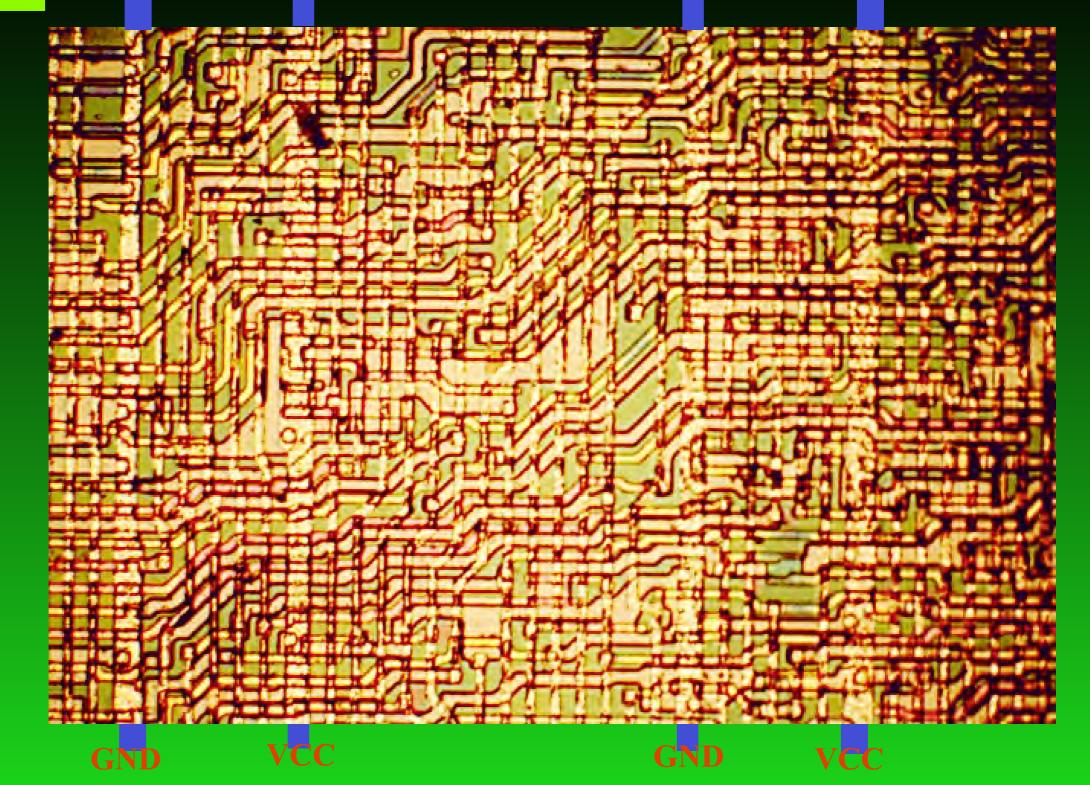

#### **Full Custom**

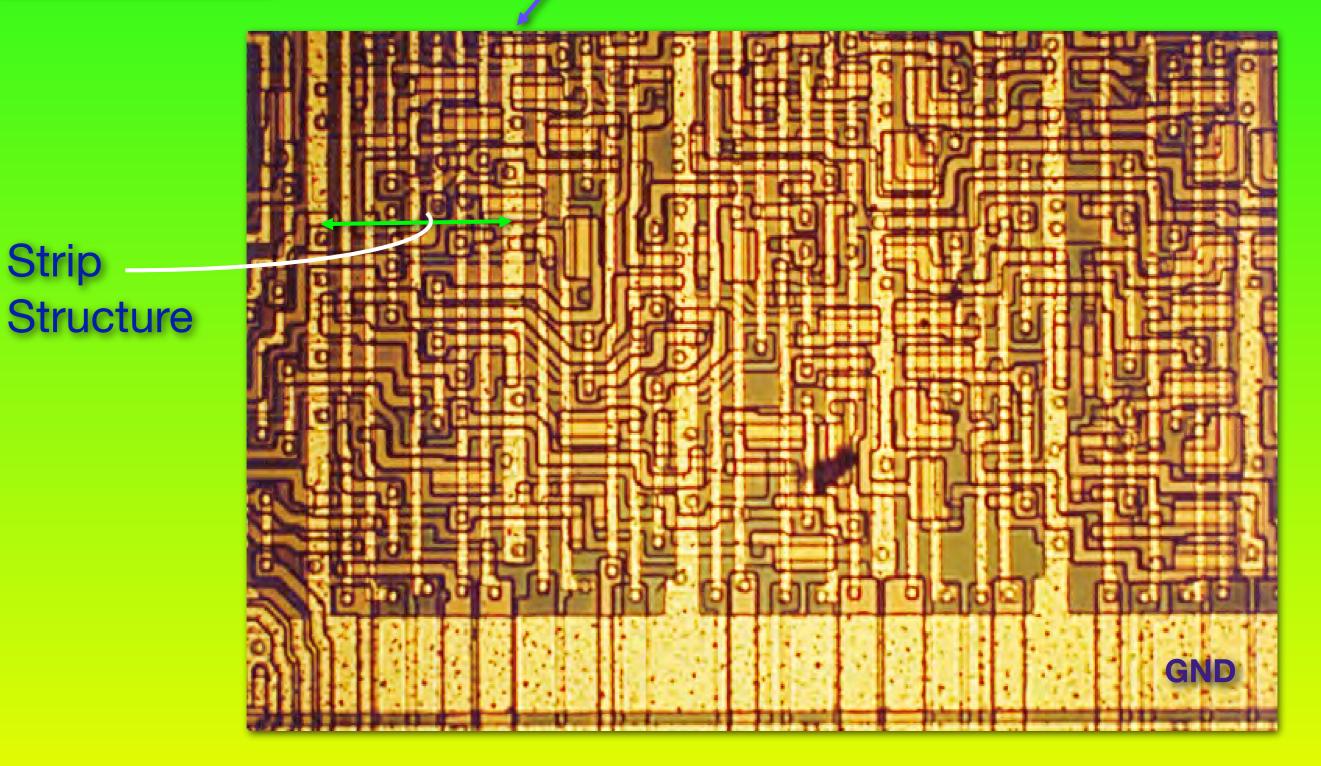

#### Zilog Z8000 detail of the control part using random logic

#### **Full Custom**

Detail of the control part of TMS7000 implemented with random logic

Change of Paradigm

Generation on-the-fly physical design as the design of a network of transistors

## Standard Cell Approach

## Cell On-the-fly Approach Transistor Level Design Automation

# Connections becomes a central problem !

Challenge: how to reduce wirelength?

### Challenge:

### how to reduce wirelength?

- area reduction

- use of complex gates (SCCG)

- improvement of routing and placement algorithms

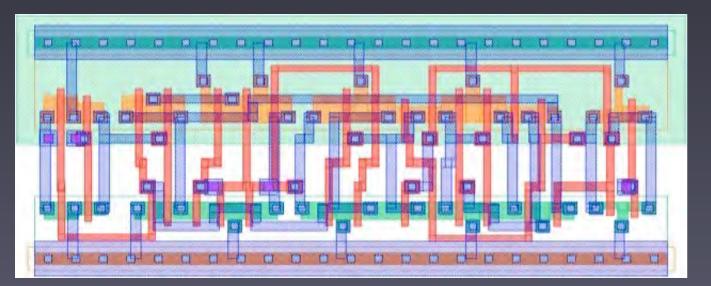

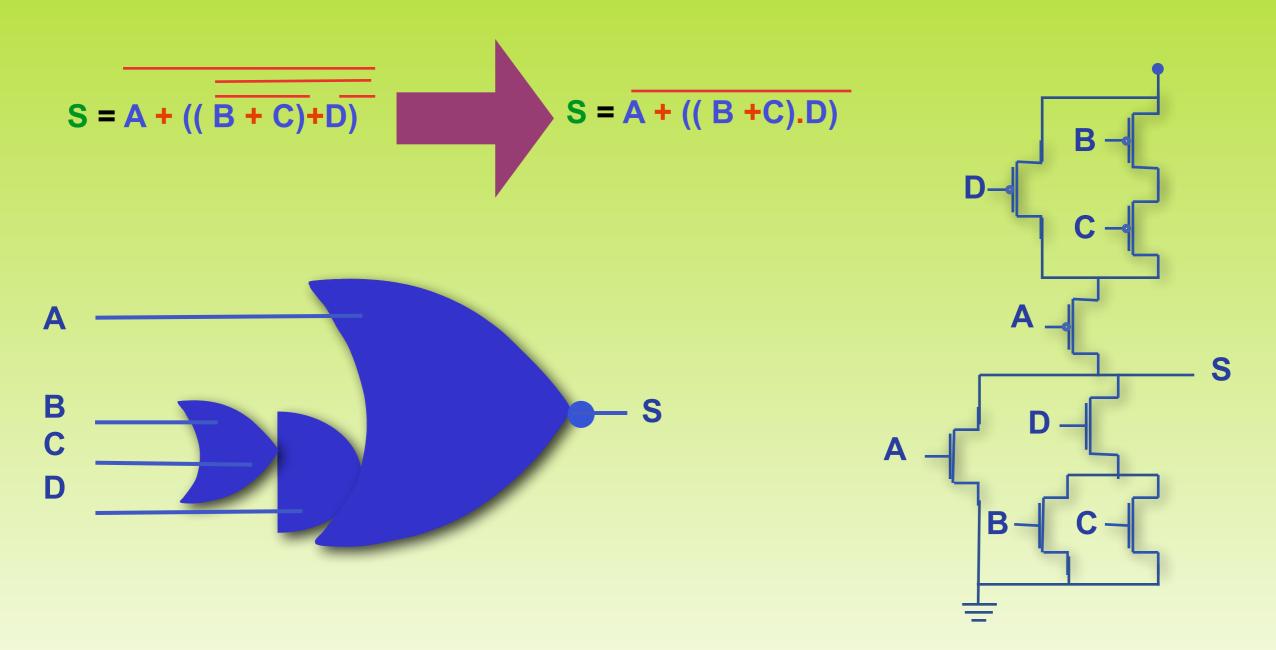

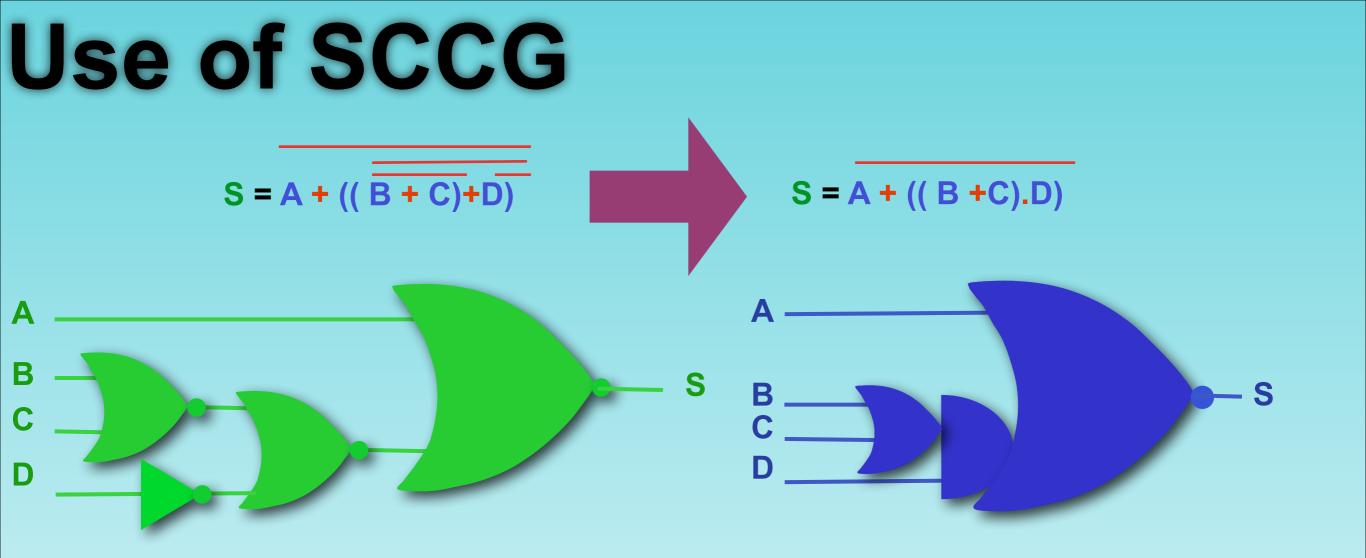

### Using Static CMOS Complex Gates (SCCG) with cell generation on-the-fly

#### It is possible do to an extreme logic minimization

### Freedom to Logic Designers !!!!

#### Automatic Layout Synthesis Using Complex Gates (SCCG)

#### NUMBER OF STACKED PMOS TRANSISTORS

|           |   | 1 | 2  | 3    | 4     | 5      |

|-----------|---|---|----|------|-------|--------|

|           | 1 | 1 | 2  | 3    | 4     | 5      |

| AOS<br>RS | 2 | 2 | 7  | 18   | 42    | 90     |

|           | 3 | 3 | 18 | 87   | 396   | 1677   |

|           | 4 | 4 | 42 | 396  | 3503  | 28435  |

|           | 5 | 5 | 90 | 1677 | 28435 | 125803 |

STACKED NMO

**NUMBER OF**

E. Detjens et al., Technology Mapping in MIS, ICCAD 1987

#### Example

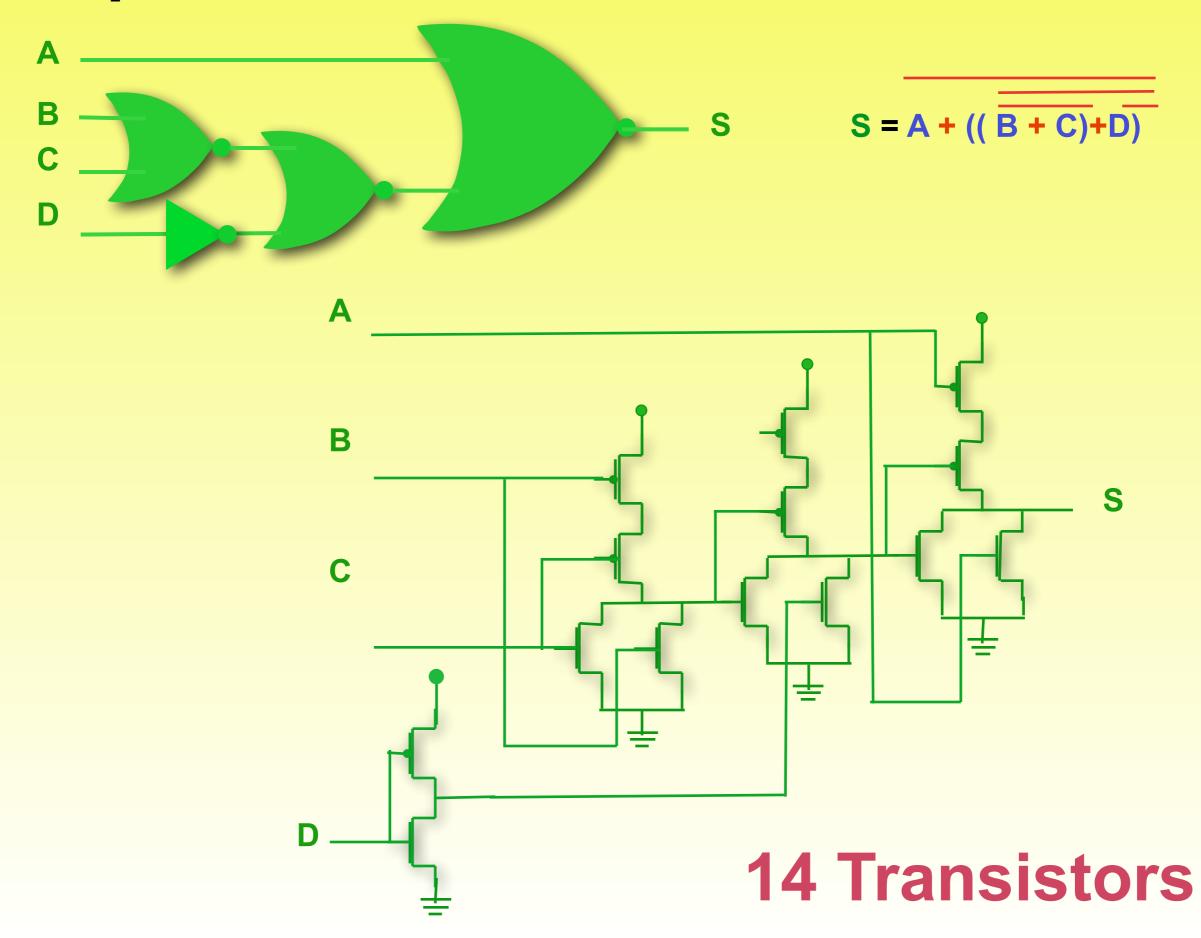

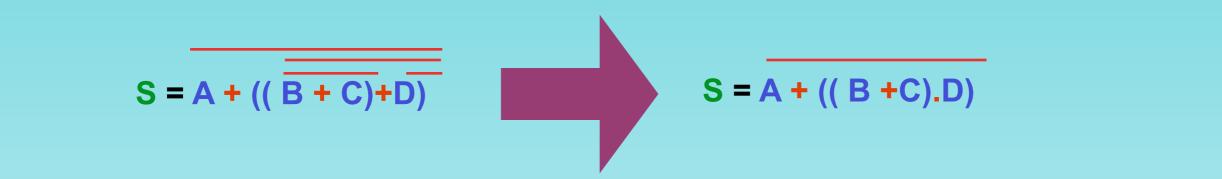

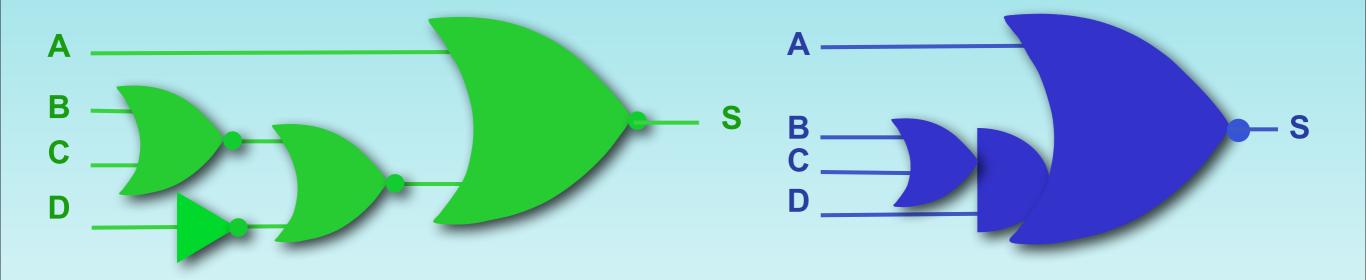

### **Use of SCCG**

#### **8 Transistors**

### **Use of SCCG**

#### **14 Transistors**

### **8 Transistors**

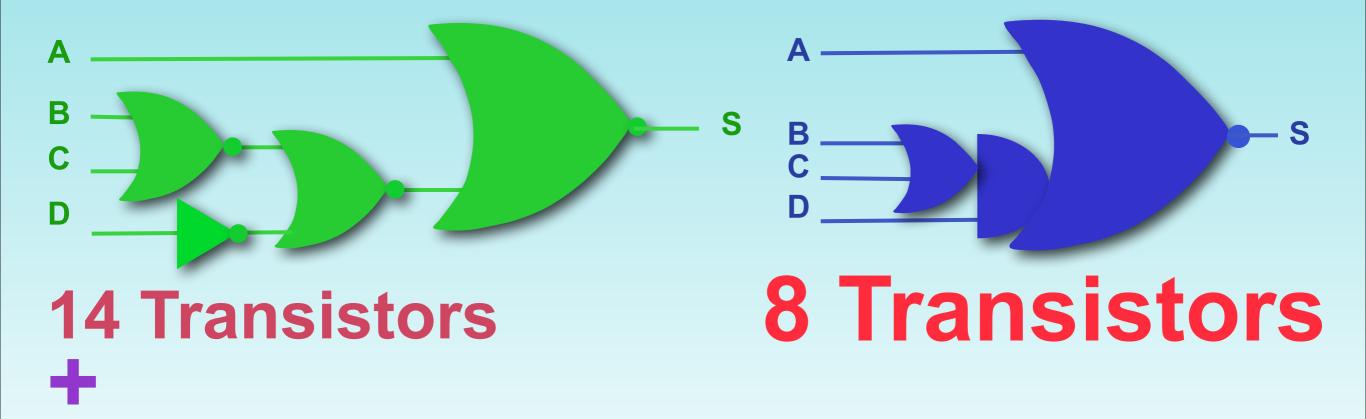

## LESS TRANSISTORS MEANS LESS

### LEAKAGE POWER

### Use of SCCG

**3 internal connections**

## LESS TRANSISTORS ALSO MEANS LESS

### CONNECTIONS

## ALSO LESS Logic Cells MEANS LESS

### CONNECTIONS

14 Transistors

8 Transistors

3 connections less

means also less VIAS

### LESS CONNECTIONS ALSO MEANS MORE SPACE BETWEEN CONNECTIONS

## Reliability Increases

## To Increase Reliability

## It is needed to reduce CONNECTION congestions

Layout Strategies

- transistor topologies

- management of routing in all layers

- VCC and Ground distribution

- clock distribution

- contacts and vias management

- body ties management

- transistor sizing and folding

Many layout decisions can contribute to power reduction

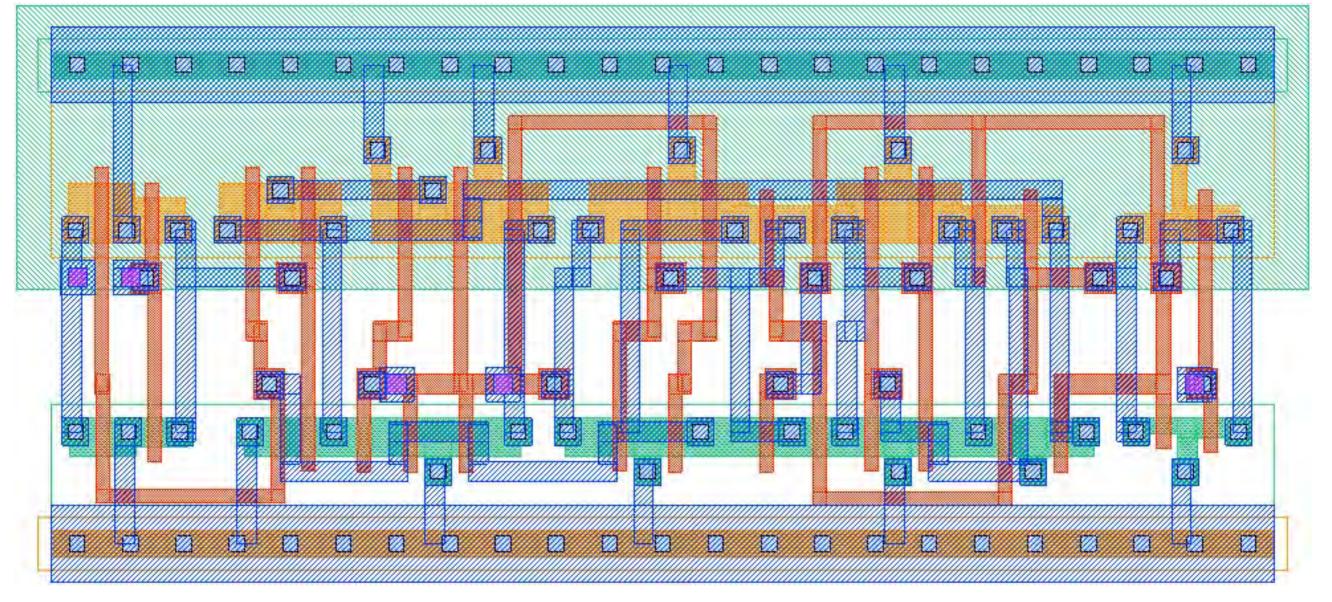

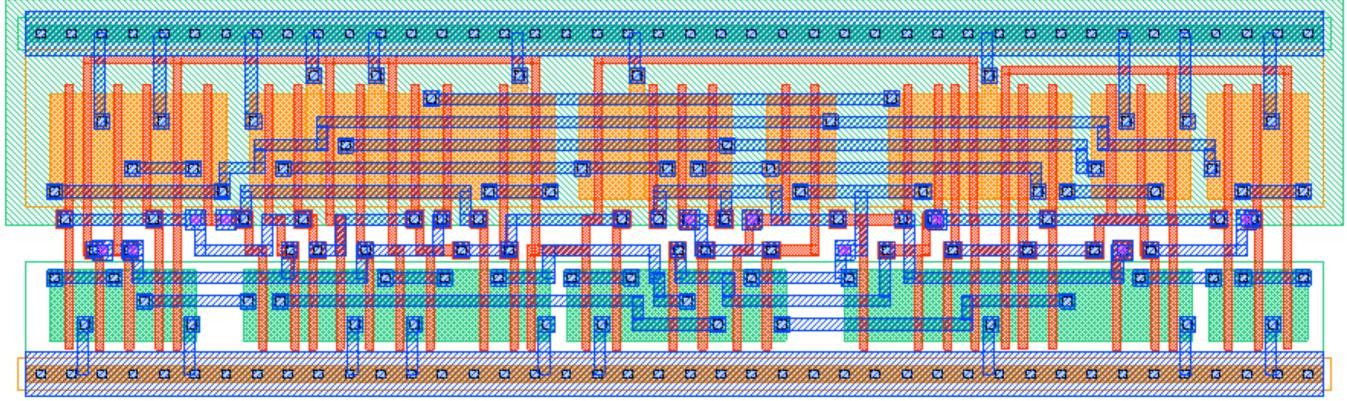

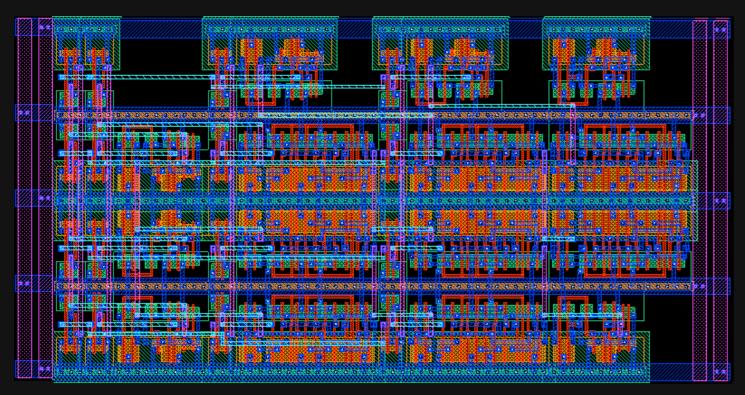

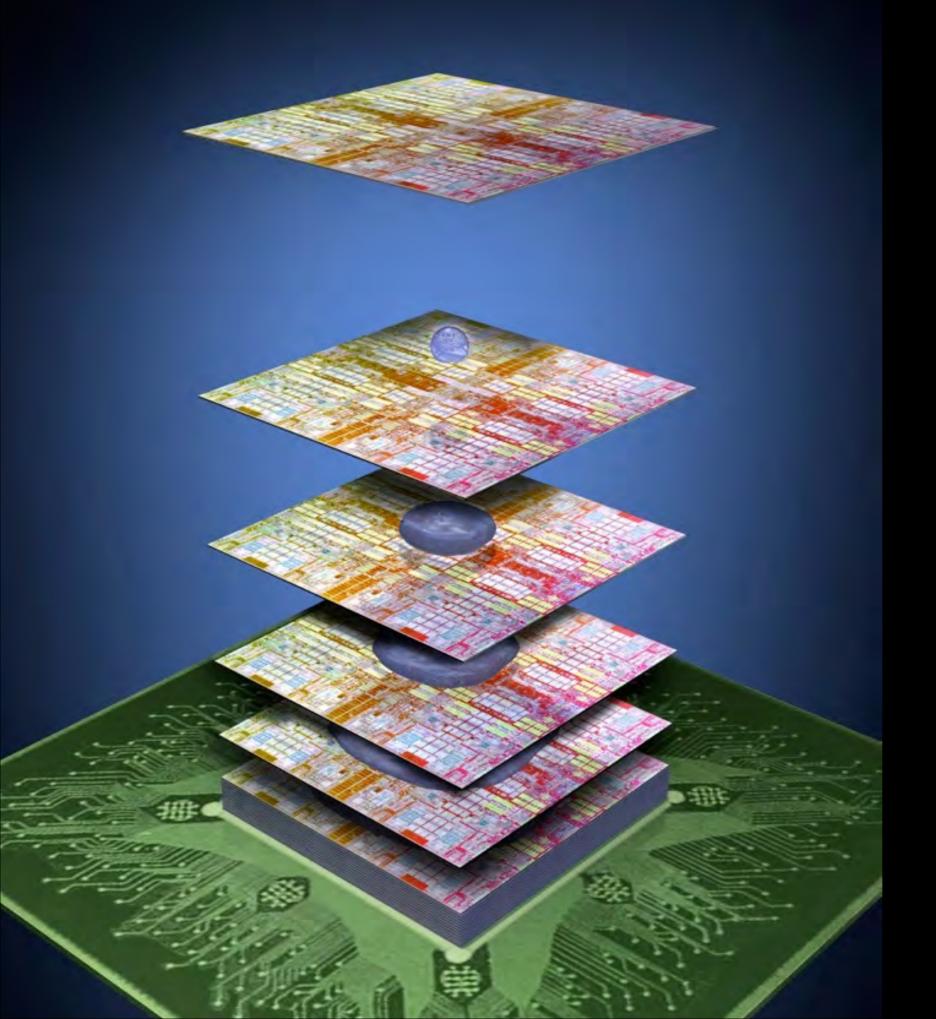

#### Layout Generated Automatically with Parrot Tool Suite

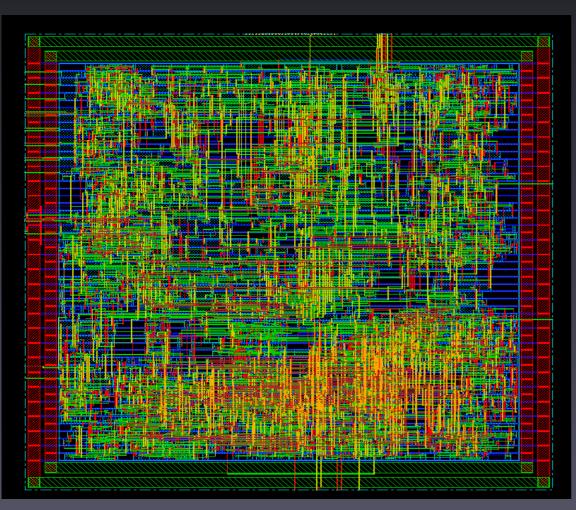

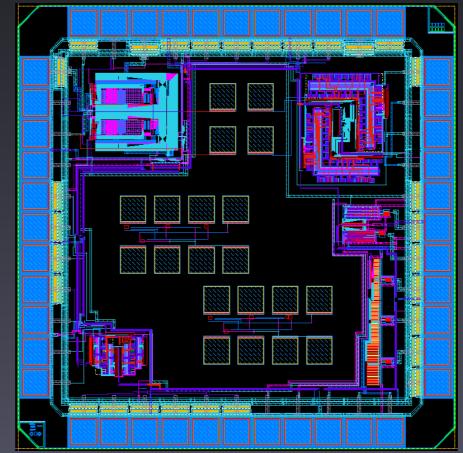

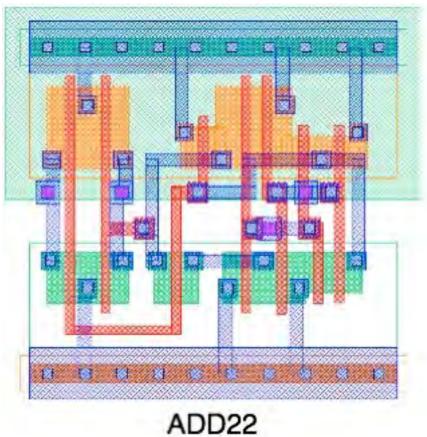

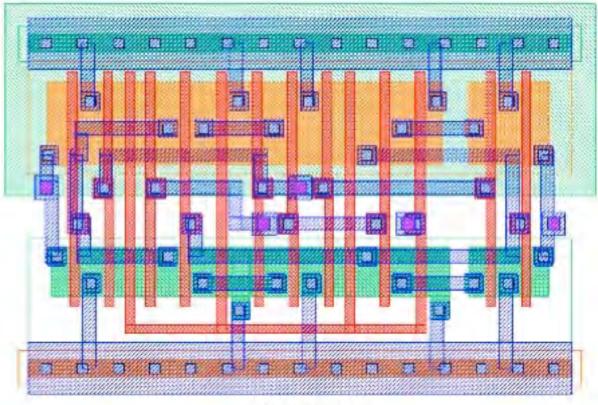

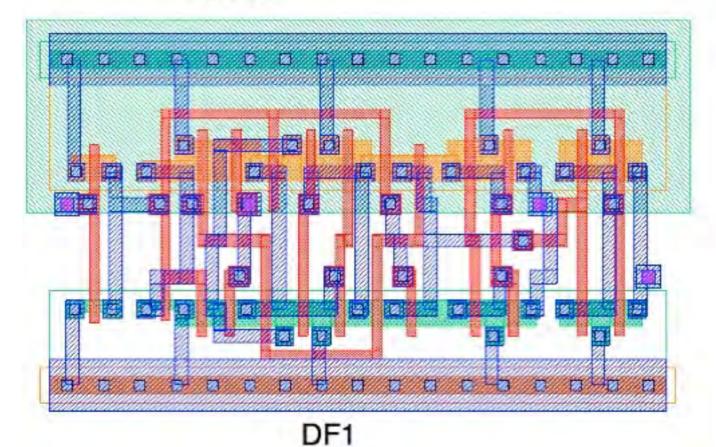

## **ASTRAN Layouts**

ADD32

## ASTRAN Layouts

JK1 (34 transistors)

#### Adder

#### Adder

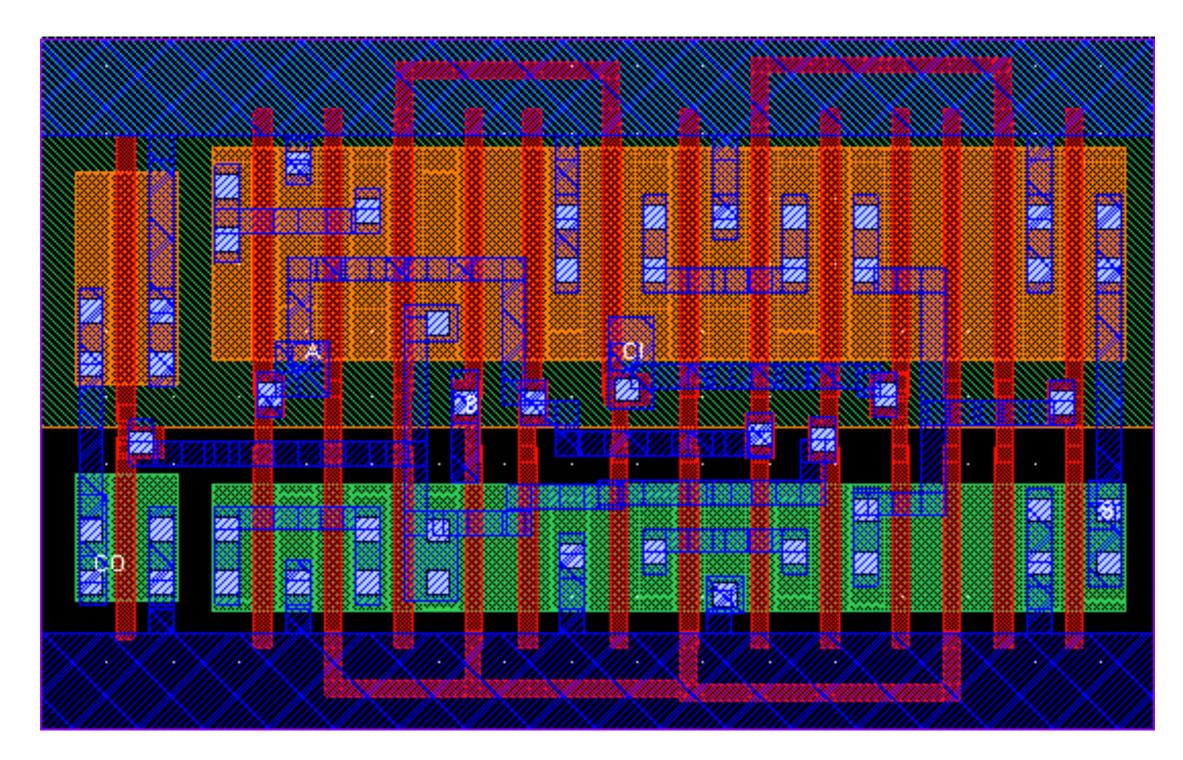

#### **ASTRAN** Layouts

#### **Non-Complementary Logic**

#### LBBDD\_0117177F177F7FFF (68 transistors)

#### Runtime: 36 min

L.S.da Rosa Jr., F.Marques, T.M.G.Cardoso, R.P.Ribas, S.S.Sapatnekar, A.I.Reis, Fast Transistor Networks from BDDs. SBCCI 2006, pp. 137-142.

#### Multiplier Carry-Save 4x4

**Generated with our Data Path Compiler**

#### **Multiplier Carry-Save 4x4**

|                       | Standard Cell | ASTRAN | Gain<br>(%) |

|-----------------------|---------------|--------|-------------|

| Number of Cells       | 52            | 28     | 46          |

| Number of Transistors | 634           | 376    | 59.3        |

| Area (µm²)            | 6716          | 5070   | 24.5        |

| Delay (ps)            | 2174          | 1896   | 12.8        |

| Power (mW)            | 6.45          | 3.97   | 61.55       |

#### 65 nm

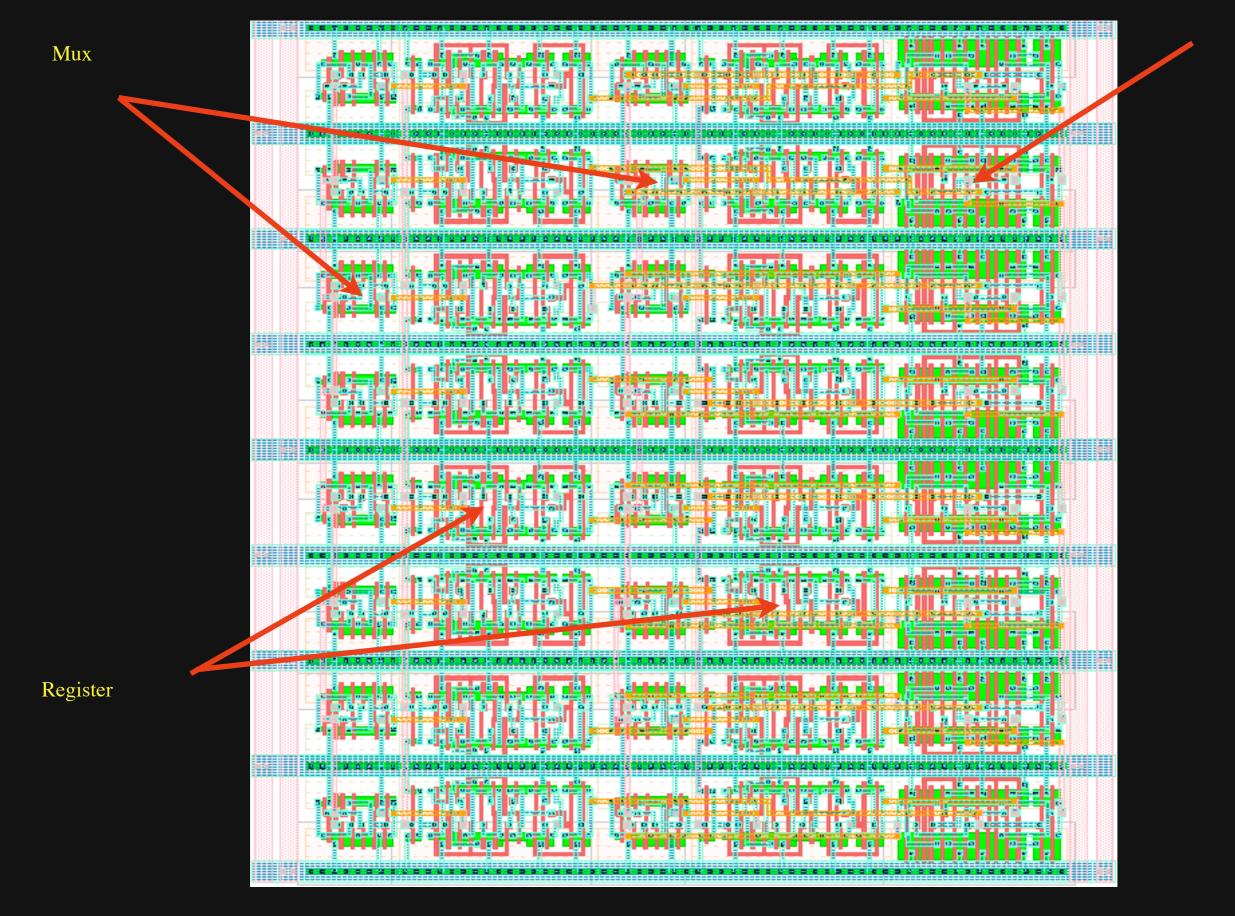

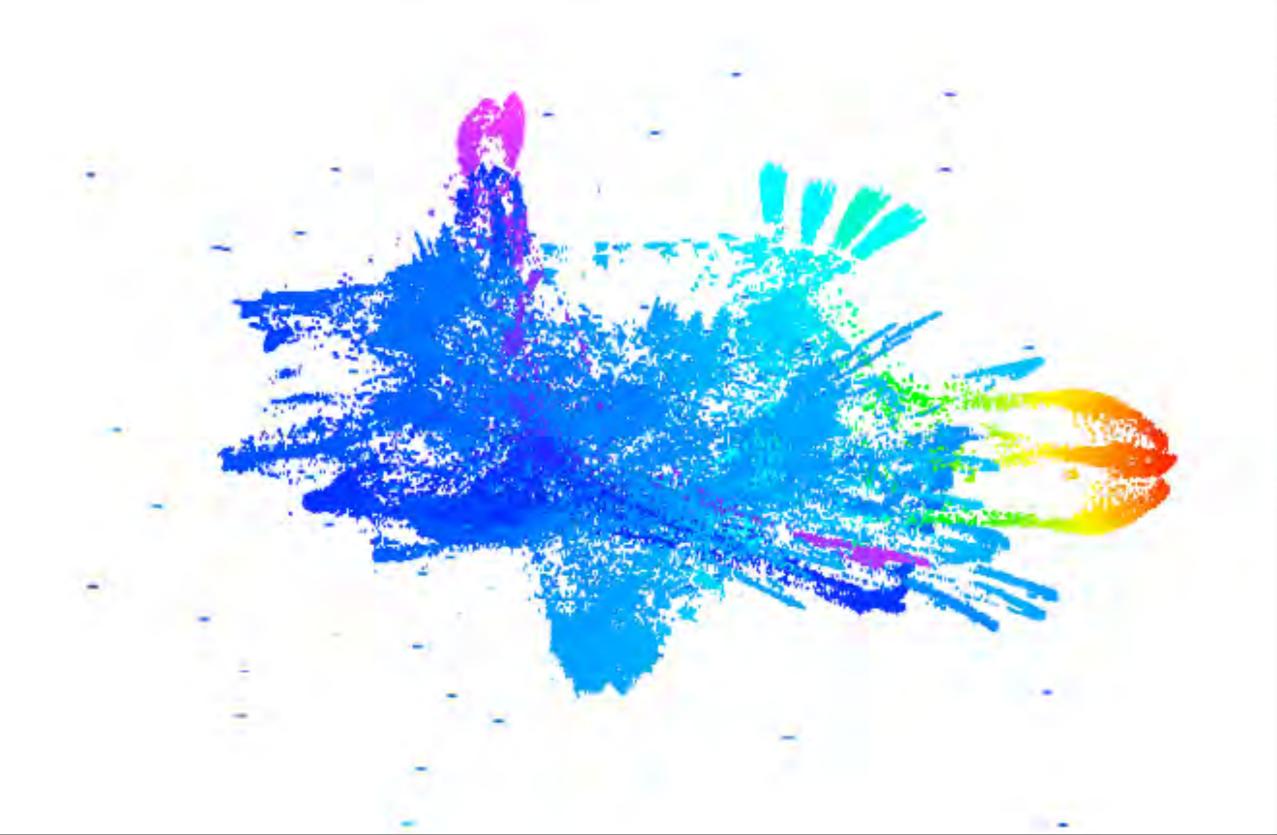

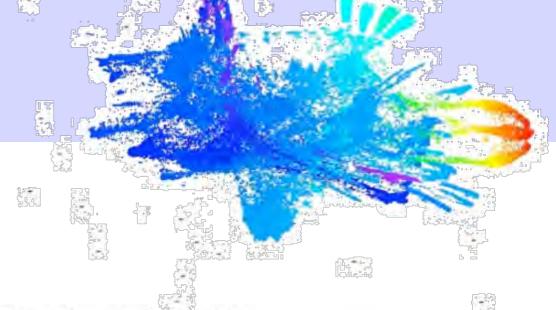

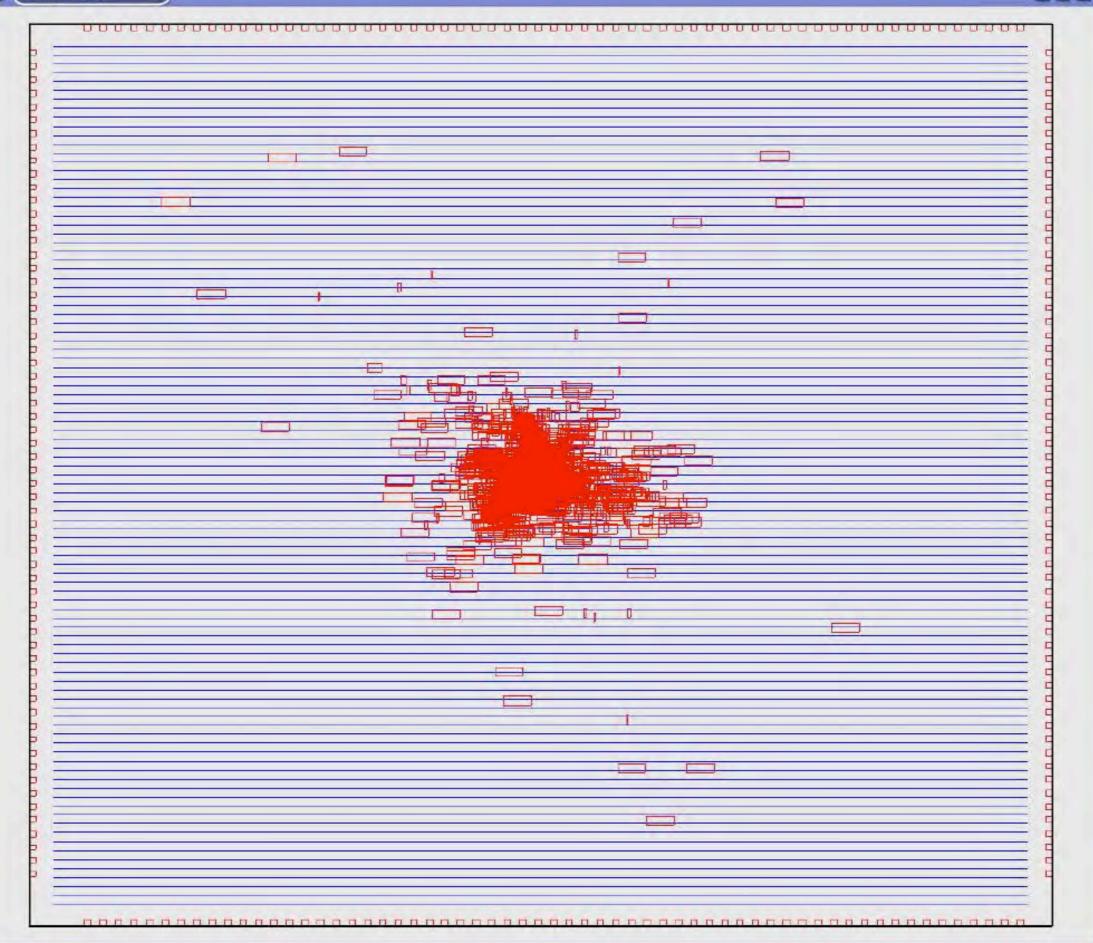

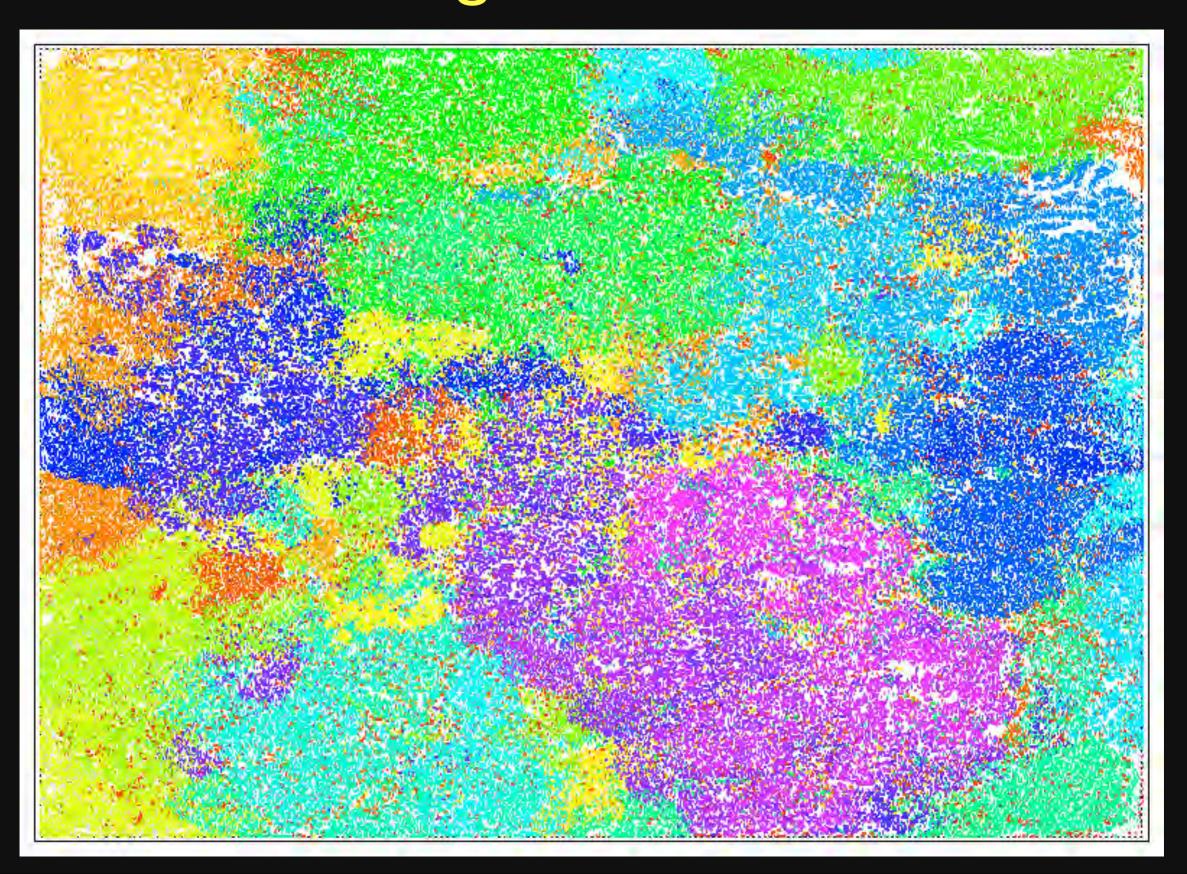

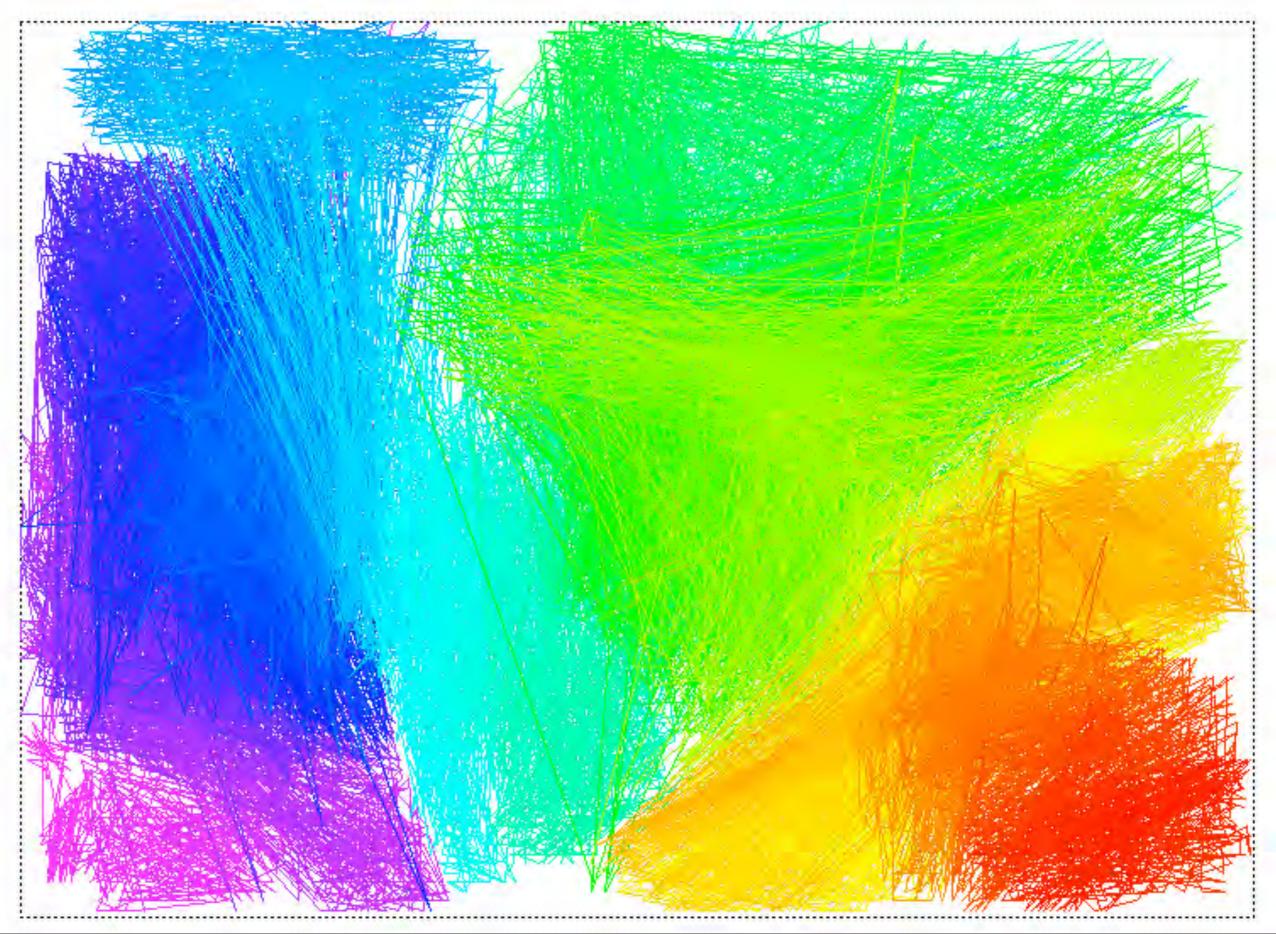

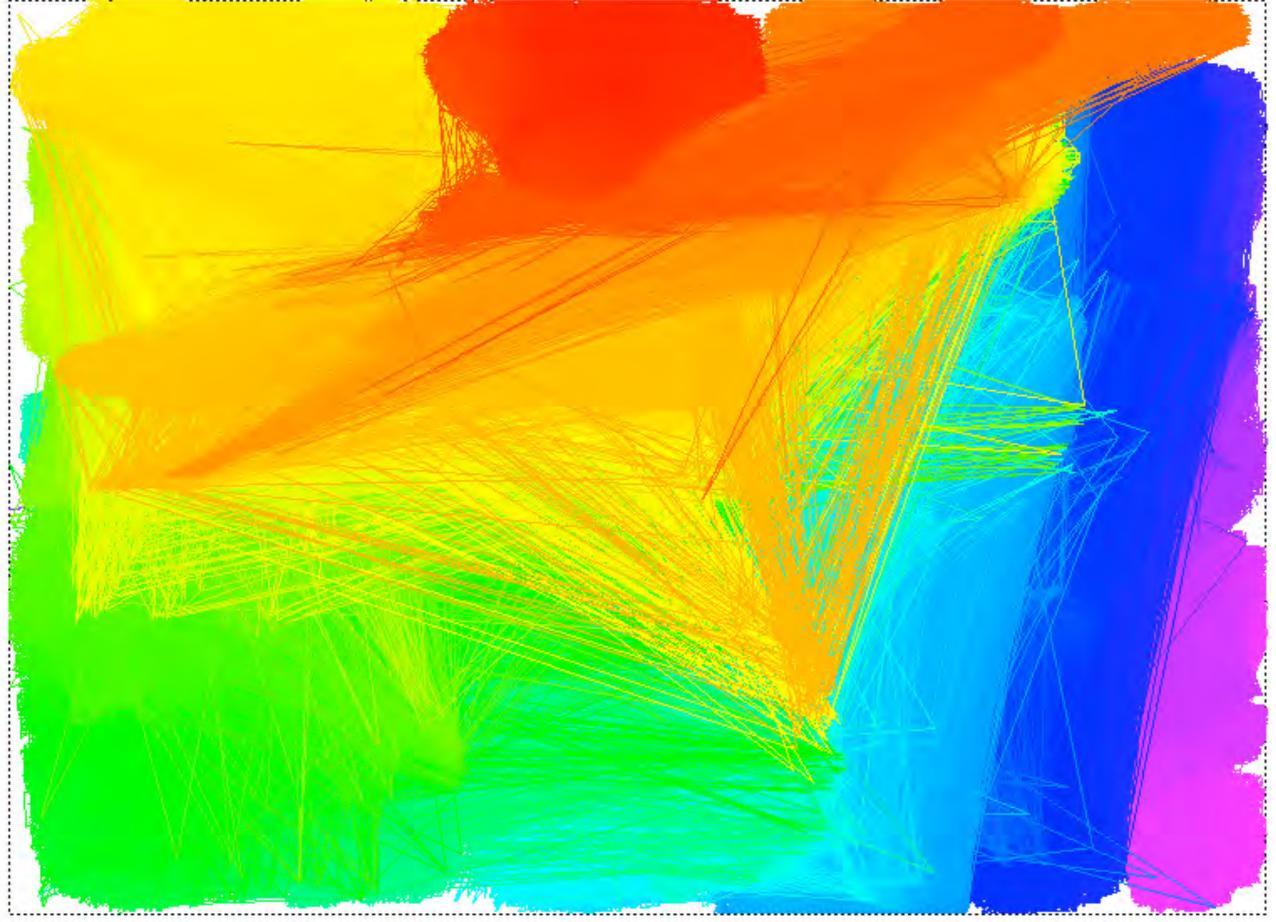

## Visualization Tools

### More on colors...

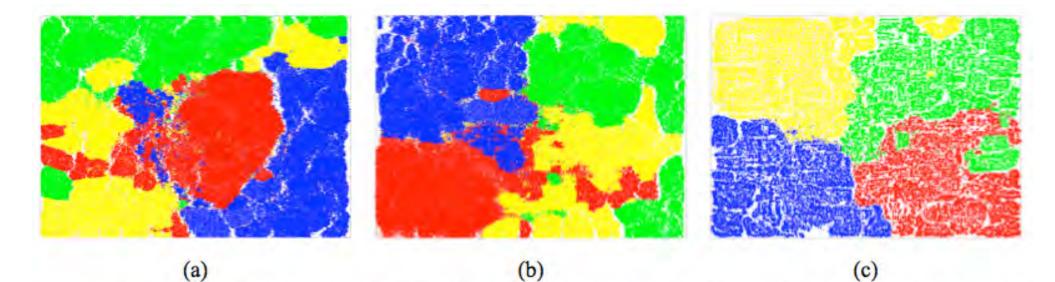

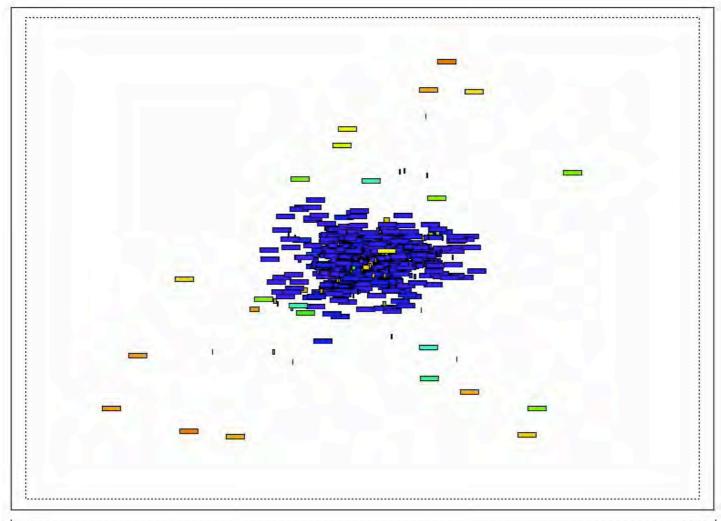

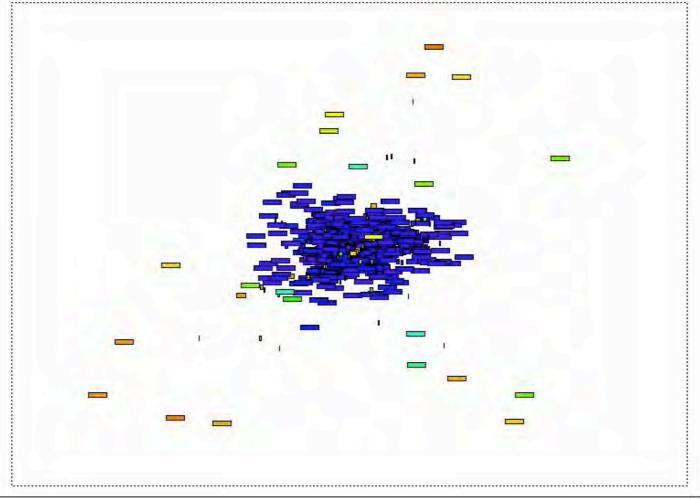

Tab.1 - Min-Cut coloring scheme. Images for ibm01 benchmark using 8 partitions.

| Capo              | Dragon            | FastPlace 3       | mPL              |

|-------------------|-------------------|-------------------|------------------|

| HPWL: 1.90689e+06 | HPWL: 1.87986e+06 | HPWL: 1.72773e+06 | HPWL: 1.6185e+06 |

|                   |                   |                   |                  |

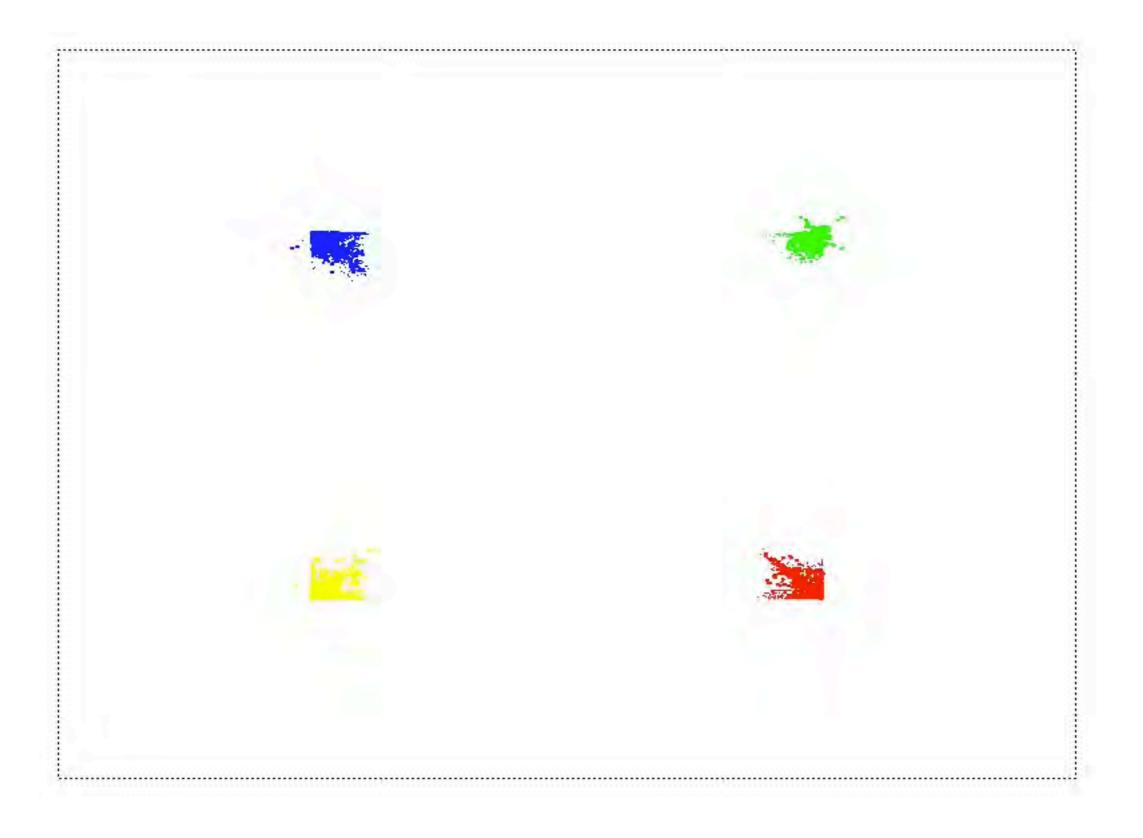

Fig. 3 – Placement coloring. (a) Our prior placer result; (b) FastPlace 3 result; (c) Our final placer result using partitioning for initial placement.

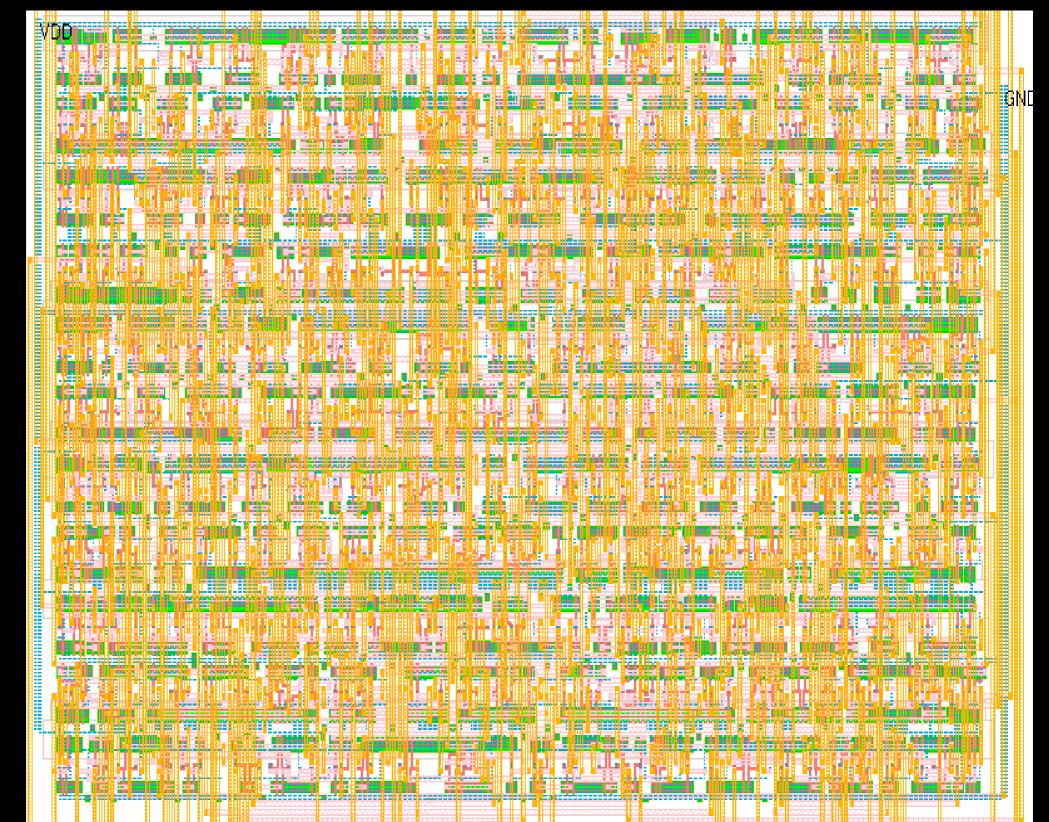

# Placement using PlaceDL

# Placement of the IBM18 circuit using UFRGS tools > 200 thousand logic cells

### **Routing Colors**

### **Routing Colors**

#### IBM**18**

#

# The second secon ON FPGAS

# B Chips

fonte: IBM

# Conclusions

more & more Power

green chips

**Optimization** in all abstraction levels Conclusions In NanoCMOS a way to reduce Power Consumption is to reduce the amount of transistors

Conclusions **Optimization on the Number** of Transistors allows: **Area reduction Reduction on the number of transistors Cell library free** Wirelength minimization **Delay Reduction Power Reduction**

# Conclusions Let's do ransistor Leve Design Automation

to reduce the amount of transistors and POWER CONSUMPTION

## **SBCCI2014**

Deadline: March 30th, 2014

27<sup>th</sup> SYMPOSIUM ON INTEGRATED CIRCUITS AND SYSTEMS DESIGN CHIP IN ARACAJU

Aracaju, BRAZIL September 1 to 5, 2014 WWW.Sbcci.org.br

#### **LASCAS 2014**

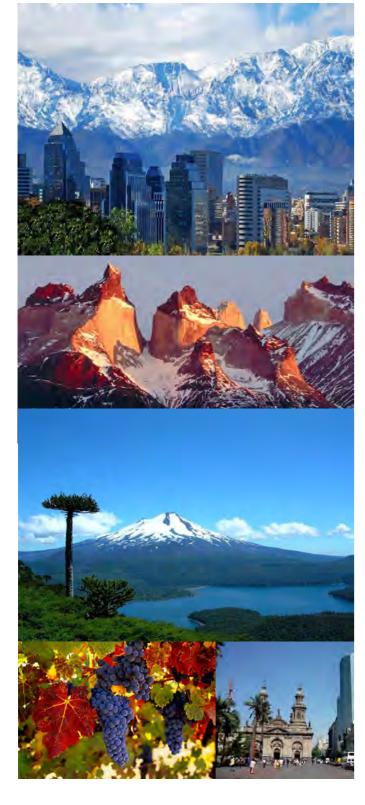

5<sup>th</sup> IEEE Latin American Symposium on Circuits and Systems Santiago, Chile February 25-28, 2014

#### www.lascas.org

**Call for Papers**

LASCAS 2014 goal is to be the International Symposium of IEEE Circuits and Systems in Latin America. Its fith edition will take place in Santiago de Chile. Santiago is the capital and economic center of Chile. With its many museums, events, theaters, restaurants, bars and other entertainment and cultural opportunities, it is also the political and cultural center of the country. Its central location makes it a great base for visiting other areas. Chile's steady economic growth has transformed Santiago into one of Latin America's most modern metropolitan area, with extensive suburban development, dozens of shopping centers, and impressive high-rise architecture. It has a modern transportation infrastructure, including the steadilygrowing Metro de Santiago. Santiago is the financial, cultural and political center of Chile and home of several regional headquarters to many multinational corporations. All this with an integration element: the friendship of its people.

The symposium will cover technical novelties and tutorial overviews on circuits and systems topics including but not limited to: Analog and Digital Signal Processing Biomedical Circuits and Systems Multimedia Systems and Applications Nanoelectronics and Gigascale Systems Cellular Neural Networks and Array Computing Neural Systems and Applications Circuits and Systems for Communications Nonlinear Circuits and Systems Computer Aided Design Power Systems and Power Electronic Circuits Sensory Systems Graph Theory and Computing • Visual Signal Processing and Communications • Life Science Systems and Applications VLSI Systems and Applications Electronic Testing

General Chair: Victor Grimblatt, Synopsys, Chile

Program Chair: Vojin G. Oklobdzija, New Mexico State University, USA Fernando Silveira, Universidad de La Republica, Uruguai

> November 1, 2013 November 1, 2013 December 13, 2013 December 27, 2013

| Paper Submission:           |

|-----------------------------|

| Special Session Proposal:   |

| Notification of acceptance: |

| Camera-ready:               |

IEEE 🤌

Deadline: November 15th, 2013

## **Green Chips**

Vancouver, November 12-13, 2013

and the second s

## Optimization is the Keyword in NanoCMOs Ricardo Reis