Version 0.01a For EDK 6.2i 24/06/2004

## 1 Goals

This document is intended for those who have a working design written in Verilog. The main principles can be extended to other languages.

- Building an OPB interface.

- Using IBM's OPB toolkit to simulate the design via OPB transactions.

- Adding the design to an EDK project.

## 2 Constructing the OPB interface<sup>1</sup>

### 2.1 What is the OPB?

The On-chip Peripheral Bus (OPB) is as bus specification designed by IBM used by Xilinx in MicroBlaze systems to communicate with peripherals. Devices on the bus are can be either masters or slaves. This document assumes that the design will be attached as a slave device.

### 2.2 The OPB protocol

The protocol described in this document is older than that used by Xilinx in the EDK, however, it allows for the design to be tested with the OPB toolkit. Slight modifications can then be made to bring the interface up to the new standard. This is addressed in section 5. An updated version of the OPB toolkit may be available with the new standard.

A typical declaration of a slave device is:

```

module opbinterface(OPB_clk, OPB_select, OPB_RNW, OPB_hwXfer, OPB_fwXfer, OPB_seqAddr, OPB_ABus, OPB_DBus, Sln_xferAck, Sln_hwAck, Sln_fwAck, Sln_errAck, Sln_toutSup, Sln_retry, Sln_DBusEn, Sln_DBus);

```

The ports beginning with OPB are inputs from the bus while the ports beginning with Sln are outputs to the bus.

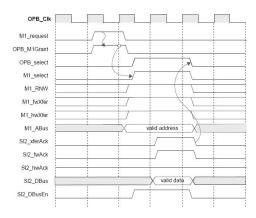

A typical transaction is shown in Figure 1.

OPB\_clk The clock at which the bus is run. Using the Xilinx Multimedia Boards, this is at 27MHz.

**OPB\_select** Driven high when OPB\_ABus and other bus signals are valid.

- **OPB\_RNW** "Read-not-write" Low when the MicroBlaze is requesting a write. High when requesting a read.

- OPB\_hwXfer, OPB\_fwXfer Used to indicate the valid bits on a write. OPB\_hwXfer is high when a halfword or a fullword is being sent. OPB\_fwXfer is high only when a fullword is being sent. These signals are replace by the byte enable signal in the OPB standard used by Xilinx.

- **OPB\_seqAddr** Indicates that the bus is requesting multiple reads or writes from sequential addresses. This is ignored in this document's treatment of the OPB protocol. If you wish to use its functionality see [1].

**OPB\_ABus** The address for which a given read or write is requested.

$<sup>^1</sup>$ It is notable that a Xilinx core exists which can interface a design with the OPB. It is accessible through the  $Edit \rightarrow Import$  Peripheral Wizard command in EDK. However currently only VHDL is supported. Since, currently, mixed language designs cannot be used as IPs in the EDK the simplest alternative is to design an interface from scratch.

Figure 1: A typical OPB transaction [1]

**OPB\_DBus** The data bus used for a write transaction.

Sln\_xferAck The response from the slave device once it has finished its part of the transaction (taking data from or putting data on the bus).

Sln\_hwAck Acknowledging a halfword transfer. (Obsolete in the OPB standard used by Xilinx)

Sln\_fwAck Acknowledging a fullword transfer. (Obsolete in the OPB standard used by Xilinx).

Sln\_errAck Set when the slave encounters an error processing a request. It is set in addition to Sln\_xferAck.

**Sln\_toutSup** Set by the slave to that its operation will occur for an extended period of time. "Timeout suppression"

Sln\_retry Set by the slave to request a retry of the transaction.

Sln\_DBusEn Set by the slave to indicate the data on Sln\_DBus is valid. (Obsolete in the OPB standard used by Xilinx).

Sln\_DBus The port used by the slave to put data on the bus during a read operation.

As implemented by Xilinx, the bus consists of a 32bit Address signal and a 32bit Data signal. Detailed descriptions of the bus signals and the transaction can be found in [1].

### 2.3 Coding the Interface

When writing the code for the interface include the parameters:

```

parameter C_BASEADDR = 32'hffffff00;

parameter C_HIGHADDR = 32'hffffffff;

```

to indicate the range of addresses that your device will respond to on the bus. These parameters will be overridden by the EDK when the device is inserted into the system. The value set in the HDL code will be useful during simulation.

## 3 Testing the OPB interface - Using IBM's CoreConnect Toolkit

#### 3.1 What is the CoreConnect Toolkit?

The CoreConnect toolkit consists of several sub-toolkits for verifying a design that uses any of various on-chip bus standards created by IBM. Of interest in this document is the OPB toolkit.

The OPB toolkit is located in CoreConnect/tk/OPB\_TOOLKIT2X.

The toolkit consists of several models to mimic the behavior of devices on the bus. The types of devices/models are Arbiter, Master and Slave. A device can be tested by connecting it to these models. The instantiation of the models and controlling their behavior is done using scripts written in the toolkit specific *OPB Bus Functional Language* that can be compiled with a compiler accompanying the toolkit.

### 3.2 Inserting the device into the toolkit

The various models used in the toolkit are found in *CoreConnect/tk/OPB\_TOOLKIT2X/verilog*. Two sets of models exist in the directory: those with the "1x" suffix and those without. The "1x" suffix is the 32bit OPB model and is the focus in this document. opb\_complex1x.v is the top-level module within which the device under test can be inserted.

Before the device under test can be inserted, new signals must be created in the toolkit's HDL to accommodate the new device. Several lines must be changed to do this. Below is the output from diff indicating the changes that were made in  $opb\_complex1x.v$  to create the new signals and instantiate the device under test.

```

107a108,114

> wire

sl3_xferack;

wire

sl3_hwack;

wire sl3_fwack;

wire sl3_errack;

wire sl3_toutsup;

wire sl3_retry;

wire[ 0 : 31 ] sl_dbus_3;

270,273c278,281

< assign opb_xferack = ((sl0_xferack | sl1_xferack ) | sl2_xferack );</pre>

assign opb_hwack = ((sl0_hwack | sl1_hwack ) | sl2_hwack );

< assign opb_fwack = ((sl0_fwack | sl1_fwack ) | sl2_fwack );

< assign opb_errack = ((sl0_errack | sl1_errack ) | sl2_errack );</pre>

assign opb_xferack = ((sl0_xferack | sl1_xferack ) | sl2_xferack | sl3_xferack );

>

assign opb_hwack = ((sl0_hwack | sl1_hwack ) | sl2_hwack | sl3_hwack);

assign opb_fwack = ((sl0_fwack | sl1_fwack ) | sl2_fwack | sl3_fwack);

assign opb_errack = ((sl0_errack | sl1_errack) | sl2_errack |sl3_errack);

280,281c288,290

< assign opb_retry = ((sl0_retry | sl1_retry ) | sl2_retry );</pre>

< assign opb_toutsup = ((sl0_toutsup | sl1_toutsup ) | sl2_toutsup );</pre>

> assign opb_retry = ((sl0_retry | sl1_retry ) | sl2_retry | sl3_retry);

>

assign opb_toutsup = ((sl0_toutsup | sl1_toutsup ) | sl2_toutsup | sl3_tousup);

286c295

< always @ (m_dbus_en or m_dbus[0] or m_dbus[1] or m_dbus[2] or

sl_dbus[0] or sl_dbus[1] or sl_dbus[2] or sl_dbus_en or opb_reset)

> always @ (m_dbus_en or m_dbus[0] or m_dbus[1] or m_dbus[2] or

sl_dbus[0] or sl_dbus[1] or sl_dbus[2] or sl_dbus[3] or sl_dbus_en or opb_reset)

379c388,392

< end

>

end

always @ (sl_dbus_3)

>

sl_dbus [ 3 ] <= sl_dbus_3 [ 0 : 31 ];

end

393a407,410

```

### 3.3 Creating a test

Creating a test consists of instantiating the bus models and controlling the models' behavior. This is accomplished by compiling files written in the bus functional language (bfl) with the bus functional compiler (BFC).

The toolkit comes with several sample bff files in  $CoreConnect/tk/OPB\_TOOLKIT2X/SampleTest$ . Open sample.bff in your favorite text editor. sample.bff instantiates a bus arbiter, a master device and a slave device and simulates communication between the master and the slave. Add communications to your device by adding read and write commands below the  $set\_device$  instruction that instantiates the master. The commands below each  $set\_device$  instruction are independent of the set of commands below other  $set\_device$  instructions. Each command set is followed sequentially. A description of the bus functional language is given in [2] which can be found in  $CoreConnect/tk/OPB\_TOOLKIT2X$ .

Note that you do not need to instantiate your own device in the bfl file.

Copy sample.bfl into it parent directory and type BFC sample.bfl to compile the file. Upon running BFC for the first time, several questions will be asked. Set Verilog as the target (you can also explore the other options). The default values for most options are fine. The location of the plb\_dcl, opb\_dcl and dcr\_dcl files is CoreConnect/tk/TOOLKIT\_DCL.

After compiling, sample.v will be created. Open sample.v and add the line

```

'include "opb_dcl.inc"

```

just below the *module* line so that it will compile properly with the correct definitions.

## 3.4 Running the simulation

Compile sample.v along with the \*1x.v files and your design with a simulator of your choice (you may have to move the .inc files into the appropriate directories). Load *opb\_complex* and *sample* as the two top-level modules for the simulation.

# 4 Adding the design to a MicroBlaze system

### 4.1 Creating the base system

Open the Xilinx EDK and select  $File \rightarrow New\ Project \rightarrow Base\ System\ Builder$  and generate a MicroBlaze system<sup>2</sup>. Locate directory of your new project. A subdirectory titled pcores will exist. Your design will be placed within this directory. Build the directory tree shown in figure 2 where yourdesignname is replaced by the name with which

Figure 2: The proof directory tree

your design will appear in the EDK.

<sup>&</sup>lt;sup>2</sup>see the ECE532 labs if you unfamiliar with this process

Within the *verilog* directory place all your HDL files including any wrappers for black-box netlist files that may be included in your design.

Within the netlist directory, place any netlist files that you are including in your design. These may include edn files generated by CoreGen.

The data directory contains three text files that must be created: yourdesignname\_v2\_1\_0.bbd, yourdesignname\_v2\_1\_0.mpd, and yourdesignname\_v2\_1\_0.pao. The string "\_v2\_1\_0" in the file names are indicative of the syntax version used in the files and thus they are not free to be altered. The string "yourdesignname" in the file name must correspond to the name given to the parent directory.

- .pao "Peripheral Analyze Order" Contains references to your HDL files in an order to resolve all dependancies.

- .bbd "Black-Box Definition" A look up file containing references to netlist files.

- .mpd "Microprocessor Peripheral Description" Contains a description of the core to be important including port connections and parameters.

Details regarding the syntax of these three files is given in [3]. Sample files are given below.

### 4.2 Peripheral Analyze Order

```

## A Header section

##

##

##

##

## Some Comments

##

lib yourdesignname sin_evaluator

lib yourdesignname add_19_19_20_bit

lib yourdesignname add_37_26_37_bit

lib yourdesignname c_k_shift

lib yourdesignname ClkGen

lib yourdesignname datamemory

lib yourdesignname genmult_7_21_22

lib yourdesignname genmult_16_18_20

lib yourdesignname genmult_20_7_28

lib yourdesignname mult_7_21_21

lib yourdesignname mult_16_18_19_bit

lib yourdesignname mult_20_7_27_bit

lib yourdesignname sub_19_19_20_bit

lib yourdesignname theta_shift

lib yourdesignname datafifo

lib yourdesignname Accumulator

lib yourdesignname DataSelector

lib yourdesignname InnerProduct

lib yourdesignname FunctionEvaluator

lib yourdesignname Pipeline

lib yourdesignname Controller

lib yourdesignname OpbInterface

```

The pao file contains references to all your HDL files including netlist wrappers. The order of the references reflects the order required to resolve dependencies with the top-level design listed last. Note that the references do not include the extension such as ".v".

#### 4.3 Black-Box Definition

The *bbd* file includes references to all the netlist files used by your design that should be in the *netlist* directory. The two required parts of the file are the line with the string "Files" followed by a comma delimited list of the netlist files. Note that, unlike in the *pao* file, the file names listed include their extensions.

```

Microprocessor Peripheral Description

##

## Comments

##

##

BEGIN OpbInterface

## Peripheral Options

OPTION IMP_NETLIST = TRUE

OPTION HDL = VERILOG

OPTION CORE_STATE = ACTIVE

OPTION ARCH_SUPPORT = virtex2:virtex2p

OPTION IPTYPE = PERIPHERAL

OPTION STYLE = MIX

## Bus Interfaces

BUS_INTERFACE BUS = SOPB, BUS_STD = OPB, BUS_TYPE = SLAVE

## Generics for VHDL or Parameters for Verilog

PARAMETER C_BASEADDR = 0xffffffff, MIN_SIZE = 0x100, BUS = SOPB

PARAMETER C_HIGHADDR = 0x00000000, BUS = SOPB

PARAMETER OPB_WIDTH = 0x00000020

## Ports

PORT OPB_clk = "", DIR = I, SIGIS = CLK, BUS = SOPB, DEFAULT =

PORT OPB_RNW = OPB_RNW, DIR = I, BUS = SOPB, DEFAULT = OPB_RNW

PORT OPB_select = OPB_select, DIR = I, BUS = SOPB, DEFAULT = OPB_select

PORT OPB_hwXfer = "", DIR = I, DEFAULT = net_vcc

PORT OPB_fwXfer = "", DIR = I, DEFAULT = net_vcc

PORT OPB_seqAddr = OPB_seqAddr, DIR = I, BUS = SOPB, DEFAULT = OPB_seqAddr

PORT OPB_ABus = OPB_ABus, DIR = I, VEC = [0:(OPB_WIDTH-1)], BUS = SOPB, DEFAULT = OPB_ABus

PORT OPB_DBus = OPB_DBus, DIR = I, VEC = [0:(OPB_WIDTH-1)], BUS = SOPB, DEFAULT = OPB_DBus

PORT Sln_errAck = Sl_errAck, DIR = 0, BUS = SOPB, DEFAULT = Sl_errAck

PORT Sln_retry = Sl_retry, DIR = 0, BUS = SOPB, DEFAULT = Sl_retry

PORT Sln_toutSup = Sl_toutSup, DIR = 0, BUS = SOPB, DEFAULT = Sl_toutSup

PORT Sln_xferAck = Sl_xferAck, DIR = 0, BUS = SOPB, DEFAULT = Sl_xferAck

```

### University of Toronto Integrating a Verilog design into a MicroBlaze System

```

PORT Sln_DBus = Sl_DBus, DIR = 0, VEC = [0:(OPB_WIDTH-1)], BUS = SOPB, DEFAULT = Sl_DBus

PORT Sln_hwAck = "", DIR = 0, DEFAULT =

PORT Sln_fwAck = "", DIR = 0, DEFAULT =

END

```

The meaning of each part of the file can be found in [3], however, below is a brief description of some notable lines.

The BEGIN line is used to indicate the file that includes the top-level module.

$OPTION\ STYLE = MIX$  indicates that the design includes both HDL files and netlist files. If the design does not include any netlist files, the option should be changed to  $OPTION\ STYLE = HDL$ .

The lines beginning with PARAMETER are used to give the EDK access to parameters within the top-level module. The values given to the parameters within the mpd file are the default values. The parameters listed in the file can be altered using the EDK's GUI.

The *Ports* section of the file lists the ports of the top-level module and to what the ports should be connected when the imported into the EDK. Listed ports can be left unconnected to be connected to a system net from within the EDK as is the case with  $Sln\_hwAck$  and  $Sln\_fwAck$  in the above example.

### 4.5 Adding the core to the base system

If the EDK was open while you created the file in the *data* directory, the EDK will have to be restarted since it refreshes its list of possible peripherals upon startup.

With the EDK project that was created earlier open, select the menu item  $Project \rightarrow Add/Edit\ Cores...$

A dialog box will appear. In the right will be a listbox of available peripherals. Scroll through this list to find the name given to your design in place of *yourdesignname* in the directory tree. Select your design and click the *Add* button so that it appears in the table on the left of the dialog box.

Change the Base Address and High Address corresponding to your design. This will be the address range available to your design in the memory addressable space. Changing values here alter the values of the  $C\_BASEADDR$  and  $C\_HIGHADDR$  parameters in the top-level module of the design.

Click on  $Bus\ Connections$  to switch tabs. Locate your design in the table on the left. Click within the box corresponding to the intersection between your design and  $mb\_opb$  so that an "s" appears in the box. This connects your device to the MicroBlaze's OPB as a slave device.

Click on *Ports* to switch tabs. Several of your designs ports were connected automatically due to what was done in the *Bus Connections* tab. Additional ports must be connected. Locate your device and associated unconnected ports in the listbox on the right of the dialog box. Select the signals you which to connect and add them to the table on the left using the << Add button. It is required that you add *OPB\_clk*. If you created the OPB interface based on the older OPB specification used by the OPB toolkit the two signals *OPB\_hwXfer* and *OPB\_fwXfer* will need to be added. After adding the signals, they will be listed in the table on the left of the dialog box. Change the net name to which each is connected. *OPB\_clk* should be connected to *sys\_clk\_s*. Connecting both *OPB\_hwXfer* and *OPB\_fwXfer* to *net\_vcc* sends the signal to your device that all data sent to it will be as full-word transfers (32 bits). If this is inappropriate (that is, you desire data of different sizes will be sent), you may wish to alter your OPB interface to use the Byte-Enable scheme implemented by Xilinx (see section 5).

Click on *Parameters* to switch tabs. Selecting your design from the drop-down list in the upper right of the dialog box lists available parameters that were made available in the .mpd file. The values of these parameters can be changed by selecting them and adding them to the table in the left of the dialog.

Click OK to finish adding the device to the system.

#### 4.6 Adding Software to the system

Adding software to the system is cover well in the Lab guides. It is notable, however, to ensure that optimizations are disabled for code communicating to your device.

# 5 Migrating to the Xilinx OPB standard

As mentioned earlier, Xilinx uses a slightly different OPB standard than the standard the IBM's toolkit available to connect. Xilinx calls devices that use the older OPB standar "legacy devices" in their documenation. The above method of connecting a legacy device is acceptable if it can be assured that the software interacting with the device will only send data in full word transfers. This may not always be the ideal. In this case, the OPB interface must be adjusted to support the OPB standard implemented by Xilinx.

### University of Toronto Integrating a Verilog design into a MicroBlaze System

The Xilinx standard does away with the following output slave signals: Sln\_hwAck, Sln\_fwAck, Sln\_DBusEn

The Xilinx standard replaces the *OPB\_hwXfer*, *OPB\_fwXfer* signals with a single 4-bit wide *OPB\_BE* byte-enable signal. The *OPB\_BE* signal extends the dynamic bus sizing available in the OPB standard. Each bit of *OPB\_BE* corresponds to a "byte lane" in the data bus signals. A bit value of 1 corresponds to the byte lane having valid data. Bit 0 of *OPB\_BE* corresponds to valid data in the bits 0:7 of *OPB\_DBus*, and so on. Thus a full-word transfer would be indicated by *OPB\_BE* being equal to the binary value 1111. A visual presentation of valid *OPB\_BE* values can be found in [4] within the section *Specifications for OPB Usage in Xilinx-developed OPB Devices*.

These changes can usually be made with relative ease. A new port entry must be added to connect the  $OPB\_BE$  signal in the .mpd file.

## References

- [1] IBM. On-Chip Peripheral Bus Architecture Specifications Version 2.1.

- [2] IBM. OPB Bus Functional Model Toolkit User's Manual.

- [3] Xilinx. Embedded System Tools Guide.

- [4] Xilinx. MicroBlaze Hardware Reference Guide.