# Simplifying System-on-Chip Design through Architecture and System CAD Tools

by

### **Lesley Shannon**

A Thesis submitted in conformity with the requirements for the Degree of Doctor of Philosophy,

Department of Electrical and Computer Engineering,

University of Toronto

# Simplifying System-on-Chip Design through Architecture and System CAD Tools

Lesley Shannon

Doctor of Philosophy,

2006

Department of Electrical and Computer Engineering University of Toronto

### **Abstract**

Historically designers created computing systems by combining Integrated Circuits (ICs) on Printed Circuit Boards (PCBs), whereas now they are able to form complete Systems-on-Chip (SoCs). For the purpose of this study, SoCs are defined as a collection of functional units on one chip that interact to perform a desired operation. These modules are typically of a coarse granularity to promote reuse of previously designed Intellectual Property (IP). The decreasing size of process technologies enables designers to implement increasingly complex SoCs using both Application Specific Integrated Circuits (ASICs) and Field Programmable Gate Arrays (FPGAs). The impact of increasing design complexity is increased design time and costs for electronics. Therefore, this research investigates methods to facilitate the design of SoCs through both architecture and CAD tools.

This thesis has two main contributions. The first is an architectural framework for SoCs, wherein they are modelled as Systems Integrating Modules with Predefined Physical Links (SIMPPL). The strength of the model is the Computing Element (CE) abstraction that separates the module's datapath from system-level control and communications to facilitate design reuse. Although SIMPPL can be used to build SoCs for ASICs or FPGAs, using an FPGA provides designers with a reprogrammable implementation platform. Thus, our second contribution is to develop a design infrastructure that leverages the advantages of reconfigurability.

# Acknowledgements

First, I would like to my parents and my brother, Matthew: I finally did it. I know you are probably wondering what took me so long, but I finally finished. Thank you for believing that I *would* finish... eventually. Also, thank you to my extended family for your love and support, and for keeping me grounded. All work and no play makes Lesley a dull girl – and a little stir crazy.

To the many friends I have made throughout my graduate studies at the University of Toronto. SF2206, LP392 and EA306 will always hold a special place in my heart. Thank you for all the long talks, extra-curricular events and crazy antics that helped to calm the madness of a stressful environment. My door will always be open to each of you.

To my many friends outside of work. You have given me sound advice and made sure that I have remembered that the world is a beautiful place built on science, but filled with art and music. Thank you for nurturing the non-engineering parts of my soul.

Lastly, but certainly not least, I must thank my supervisor, Dr. Paul Chow. My Doctorate studies have been a fantastic experience and I know that I interminably indebted to you for this. Over the years I have seen how crucial the rapport between student and supervisor is to the graduate experience. All I can say is that if my students find me to be half as good a supervisor as you have been to me, I will consider myself a success.

I would also like to acknowledge the financial support, as well as the equipment and software donations, that I have received from the following organizations that have made this research possible: the Canadian Microelectronics Corporation, the Natural Sciences and Engineering Research Council, the O'Brien Foundation, the Ontario Government, the University of Toronto, the Walter C. Sumner Foundation, and Xilinx.

# **Contents**

| Al | bstrac  | et            |                                             | iii  |

|----|---------|---------------|---------------------------------------------|------|

| A  | cknov   | vledgme       | ents                                        | v    |

| Li | st of l | Figures       |                                             | xi   |

| Li | st of ' | <b>Fables</b> |                                             | xiii |

| Gl | lossar  | $\mathbf{y}$  |                                             | XV   |

| 1  | Intr    | oductio       | on.                                         | 1    |

|    | 1.1     | Motiv         | ation                                       | 1    |

|    | 1.2     | Object        | tive                                        | 2    |

|    | 1.3     | Contri        | butions                                     | 3    |

|    | 1.4     | Thesis        | S Organization                              | 4    |

| 2  | Mod     | lelling S     | SoCs: SIMPPL                                | 5    |

|    | 2.1     | IP Ret        | ıse                                         | 5    |

|    | 2.2     | On-Cl         | nip Communication Structures                | 6    |

|    | 2.3     | SIMP          | PL Model                                    | 7    |

| 3  | The     | Compt         | ıting Element Abstraction                   | 10   |

|    | 3.1     | SIMP          | PL Controller                               | 12   |

|    |         | 3.1.1         | Controller Architecture                     | 12   |

|    |         | 3.1.2         | Controller Instruction Set                  | 14   |

|    | 3.2     | Debug         | Controllers                                 | 18   |

|    |         | 3.2.1         | Debug-Controller Architecture and Interface | 18   |

|    |         | 3.2.2         | Debugger Options and Detectable Errors      | 20   |

|    | 3.3     | SIMP          | PL Control Sequencer                        | 21   |

|    |         | 3.3.1         | SCS Interface                               | 21   |

|    |         | 3.3.2         | Static Programming Example                  | 23   |

|    |         | 3.3.3         | Dynamic Programming Architecture            | 25   |

|    | 34      | Summ          | arv                                         | 26   |

| 4 | Imp  | lementii | ng SIMPPL SoCs                                          | 28       |

|---|------|----------|---------------------------------------------------------|----------|

|   | 4.1  | SIMPP    | PL SoC Applications                                     | 28       |

|   |      | 4.1.1    | SIMPPL SoC Implementation Statistics                    | 30       |

|   | 4.2  | CE Imp   | plementations                                           | 31       |

|   |      | 4.2.1    | Controller Implementation Statistics                    | 32       |

|   |      | 4.2.2    | CE Architectures                                        | 35       |

|   |      | 4.2.3    | CE Implementation Statistics                            | 36       |

|   | 4.3  | Detaile  | ed Analysis of an SoC Implementation                    | 38       |

|   |      | 4.3.1    | Resource Usage                                          | 38       |

|   |      | 4.3.2    | Design Time Statistics                                  | 40       |

|   | 4.4  | Summa    | ary                                                     | 42       |

| 5 | Desi | gning S  | oCs on FPGAs                                            | 43       |

|   | 5.1  |          | t Status of SoC Design for FPGAs                        | 43       |

|   |      | 5.1.1    | Systems Research using FPGAs                            | 44       |

|   |      | 5.1.2    | Commercial System Design Tools for FPGAs                | 45       |

|   | 5.2  | Movins   | g from Off-Chip Estimation to On-Chip Evaluation        | 46       |

|   |      | 5.2.1    | Simulating versus Profiling Hardware/Software Codesigns | 47       |

|   |      |          | 5.2.1.1 GNU's gprof                                     | 48       |

|   |      | 5.2.2    | Proposed Design Methodology                             | 48       |

|   |      |          | 5.2.2.1 Benefits of Designing SIMPPL SoCs using FPGAs   | 50       |

|   | 5.3  | Design   | ing SIMPPL SoCs on FPGAs                                | 51       |

|   |      | 5.3.1    | Experimental Platform                                   | 52       |

|   |      | 5.3.2    | System Generator                                        | 52       |

|   |      | 5.3.3    | On-Chip Testbed                                         | 55       |

|   | 5.4  | Summa    | ary                                                     | 56       |

| 6 | Sno  | npΡ      |                                                         | 58       |

| Ū | 6.1  | -        | al Architecture                                         | 58       |

|   | 0.1  | 6.1.1    | Design Decisions                                        | 60       |

|   | 6.2  |          | mental Evaluation                                       | 62       |

|   | 0.2  | 6.2.1    | Methodology                                             | 62       |

|   |      | 6.2.2    | Dhrystone                                               | 64       |

|   |      | 6.2.3    | AES                                                     | 70       |

|   | 6.3  |          | ary                                                     | 74       |

| 7 | WO   | oDSTO    | CV                                                      | 75       |

| ′ | 7.1  |          | CE Profiling Architecture                               | 75       |

|   | 7.1  | 7.1.1    | Bottleneck Detection                                    | 76       |

|   |      | 7.1.1    |                                                         | 79       |

|   | 7.2  |          | Implementation and Design Decisions                     | 81       |

|   | 1.4  | 7.2.1    | Methodology                                             | 81       |

|   |      | 7.2.1    |                                                         |          |

|   |      | 7.2.2    | Proposing System Example                                | 83<br>85 |

|   | 7 2  |          | Branching System Example                                | 86       |

|   | 7.3  | Summa    | ary                                                     | 00       |

| 8  | Con    | clusions and Future Work                         | 88  |

|----|--------|--------------------------------------------------|-----|

|    | 8.1    | Conclusions                                      | 88  |

|    |        | 8.1.1 SoC Architecture                           | 88  |

|    |        | 8.1.2 SoC Design Tools                           | 89  |

|    | 8.2    | Future Work                                      | 90  |

| Bi | bliogi | caphy                                            | 91  |

| A  | SIM    | PPL Controllers HDL Source Code                  | 96  |

|    | A.1    | Full Instruction Set                             | 96  |

|    | A.2    | Consumer Execute Controller                      | 97  |

|    | A.3    | Consumer Debug Controller                        | 106 |

|    | A.4    | Producer Execute Controller                      | 122 |

|    | A.5    | Producer Debug Controller                        | 130 |

|    |        | Full Execute Controller                          | 144 |

|    |        | Full Debug Controller                            | 152 |

| В  | Inpu   | nt File Format for the System Generator          | 166 |

| C  | On-    | chip Testbed Source and Sink Packet Interpreters | 168 |

|    | C.1    | Transmitter Testbed                              | 168 |

|    | C.2    | Receiver Testbed                                 | 175 |

| D  | Exe    | cution Profile Data from SnoopP Experiments      | 181 |

| E  | Sno    | opP HDL Source Code                              | 185 |

| F  | Inni   | ut File Format for WOoDSTOCK                     | 195 |

# **List of Figures**

| 2.1             | Standardizing the IP interface using (a) SIMPPL for point-to-point communications and (b) OCP for different bus standards                       | 6        |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2<br>2.3      | A generic SoC described using the SIMPPL model                                                                                                  | 8        |

| 3.1             | The concept for the hardware CE                                                                                                                 | 10       |

| 3.2             | The hardware CE abstraction                                                                                                                     | 11       |

| 3.3             | An overview of the SIMPPL controller datapath architecture                                                                                      | 13       |

| 3.4             | An internal link's data packet format                                                                                                           | 15       |

| 3.5             | A Data packet with four bypass instructions                                                                                                     | 17       |

| 3.6<br>3.7      | The SIMPPL debug controller architecture                                                                                                        | 18<br>19 |

| 3.8             | The standard SIMPPL control sequencer structure and interface to the SIMPPL controller                                                          | 22       |

| 3.9             | Pseudocode for the sensor unit's SCS program                                                                                                    | 23       |

| 3.10            | Pseudo-HDL code to implement the state machine for the sensor unit's                                                                            |          |

|                 | program counter and the valid instruction signal                                                                                                | 24       |

| 3.11            | A CE with multiple packets of data in flight                                                                                                    | 25       |

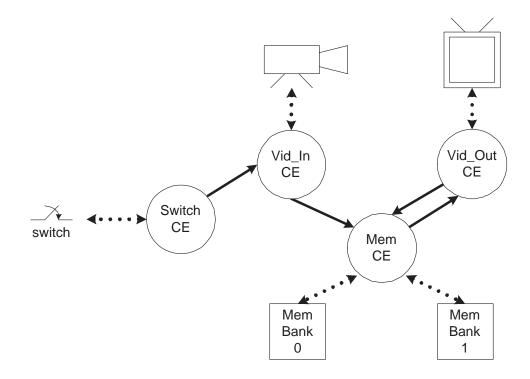

| 4.1             | The SIMPPL model for the video streaming and snapshot applications                                                                              | 29       |

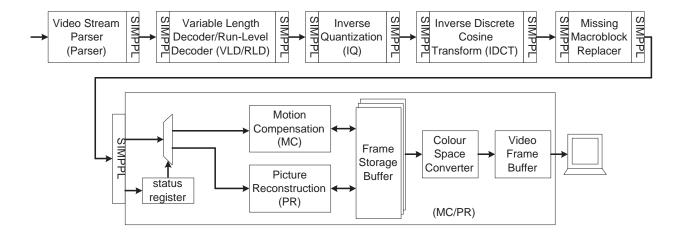

| 4.2             | The SIMPPL model for an MPEG-1 video decoder                                                                                                    | 30       |

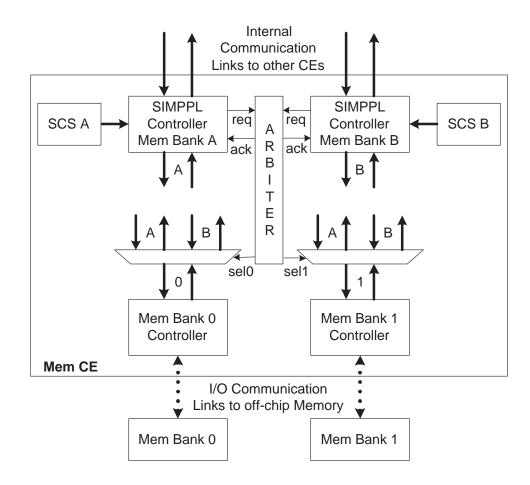

| 4.3             | The shared Computing Element architecture for a shared memory CE                                                                                | 35       |

| 4.4             | The pipelined Computing Element architecture                                                                                                    | 36       |

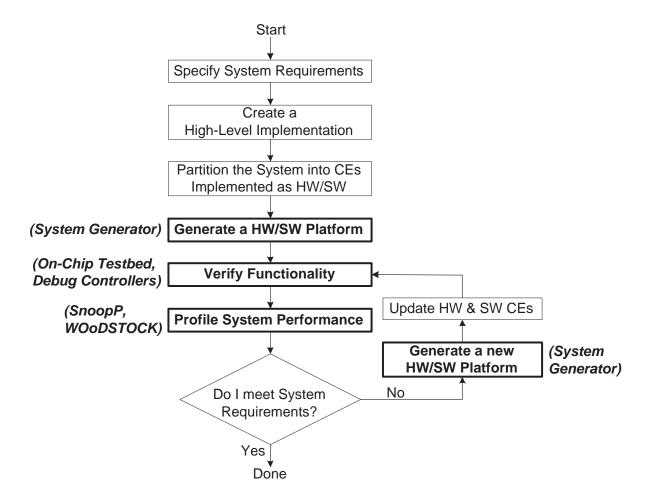

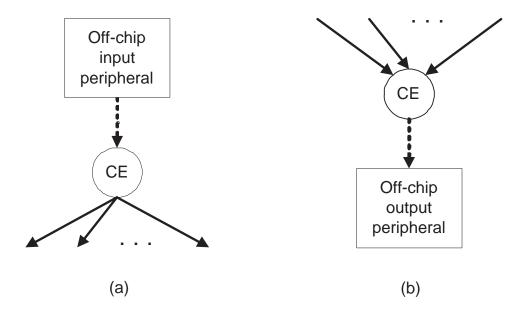

| 5.1<br>5.2      | An SoC Design Methodology for Reconfigurable Platforms                                                                                          | 49<br>53 |

| 5 2             | an off-chip output peripheral                                                                                                                   | 53<br>54 |

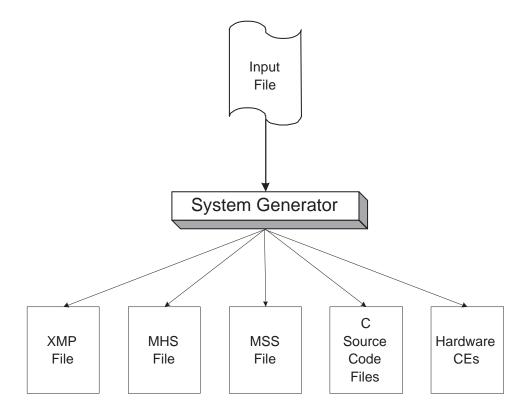

| 5.3<br>5.4      | System Generator Design Flow                                                                                                                    | 55<br>55 |

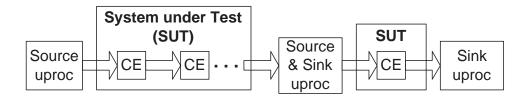

| J. <del>4</del> |                                                                                                                                                 | 33       |

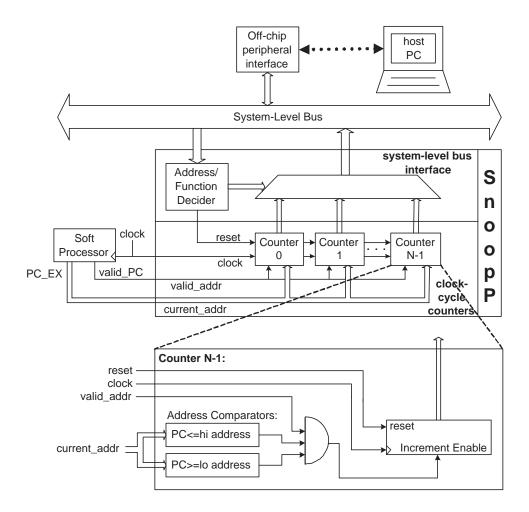

| 6.1             | The Generic SnoopP Architecture                                                                                                                 | 59       |

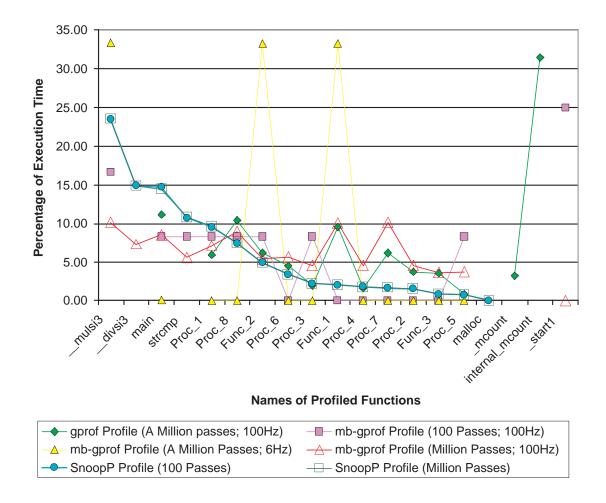

| 6.2             | Profiling Results for Dhrystone using gprof on a Sun station and mb-gprof and SnoopP on a MicroBlaze using software implementations of the mul- |          |

| - 0             | tiply and divide functions.                                                                                                                     | 66       |

|                 |                                                                                                                                                 |          |

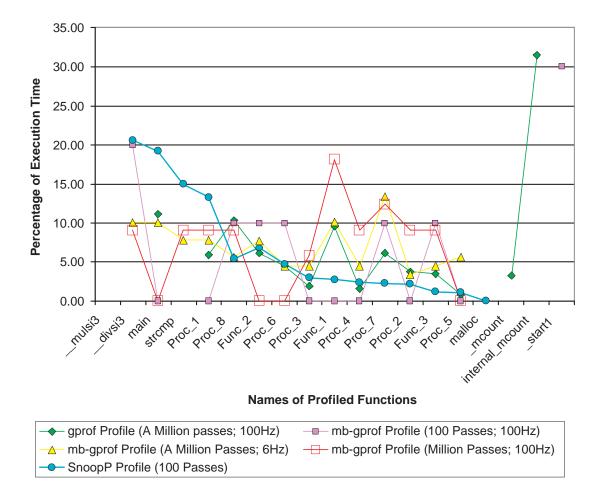

| 6.3             | Profiling Results for Dhrystone using gprof on a Sun station and mb-gprof and SnoopP on a MicroBlaze that includes a hardware multiplier and a  |          |

| 0 001                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and SnoopP on a MicroBlaze that includes a hardware multiplier and a      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| hardware divider                                                          | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

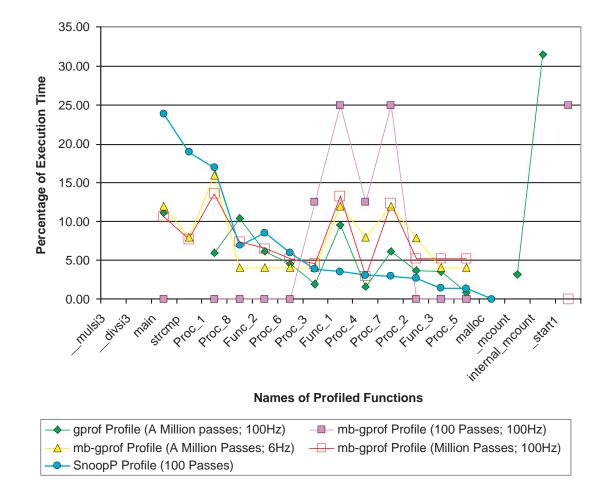

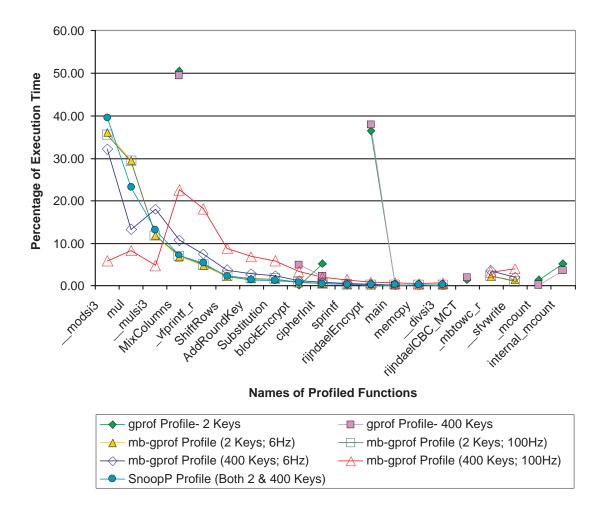

| Profiling Results for AES using gprof on a Sun station and mb-gprof and   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SnoopP on a MicroBlaze using software implementations of the multiply     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| and divide functions                                                      | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

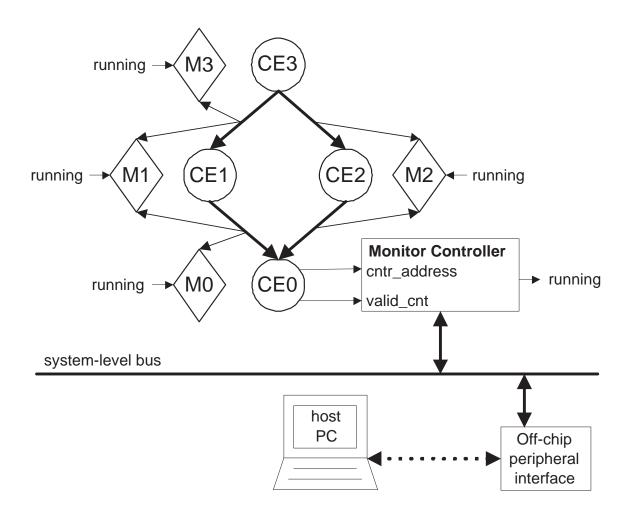

| The WOoDSTOCK architecture                                                | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

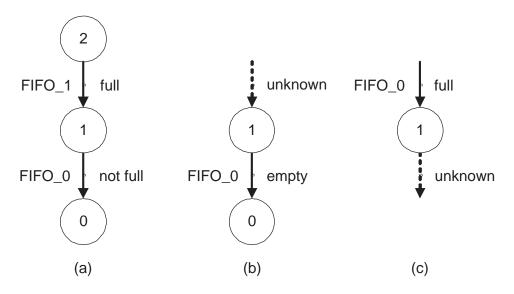

| Examples of the different types of bottlenecks detectable by WOoD-        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| STOCK: (a) interior bottleneck, (b) input bottleneck, and (c) output bot- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| tleneck                                                                   | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

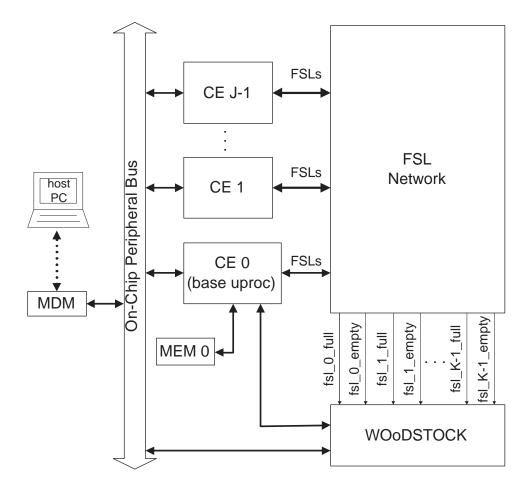

| The interface of WOoDSTOCK with the Fast Simplex Link (FSL) network       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| of a multi-CE system and a host PC via the Microprocessor Debug Module.   | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

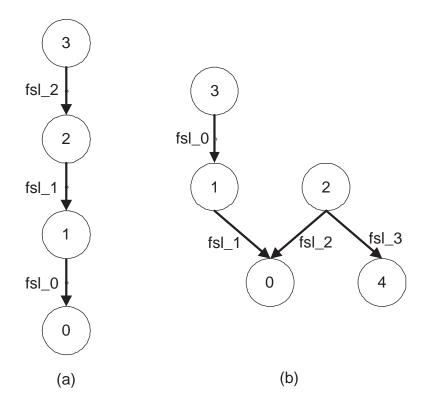

| Two application architectures described with the SIMPPL model: (a) a      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| pipelined system (b) a system with branching                              | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                           | Profiling Results for AES using gprof on a Sun station and mb-gprof and SnoopP on a MicroBlaze using software implementations of the multiply and divide functions.  The WOoDSTOCK architecture.  Examples of the different types of bottlenecks detectable by WOoDSTOCK: (a) interior bottleneck, (b) input bottleneck, and (c) output bottleneck.  The interface of WOoDSTOCK with the Fast Simplex Link (FSL) network of a multi-CE system and a host PC via the Microprocessor Debug Module.  Two application architectures described with the SIMPPL model: (a) a |

# **List of Tables**

| 3.1<br>3.2                        | The current instruction set supported by the SIMPPL controller The current error cases detectable using the debug controller                      | 16<br>20 |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1<br>4.2<br>4.3                 | Table of the System Integration times for SoCs                                                                                                    | 30<br>32 |

| т.Э                               | SIMPPL Controllers                                                                                                                                | 34       |

| 4.4                               | Implemented CEs                                                                                                                                   | 37       |

| 4.5<br>4.6                        | Table of the resource usage of the individual modules and total system Table of the CE design and integration times required for the system given | 38       |

|                                   | in person-hours                                                                                                                                   | 40       |

| 6.1                               | gprof Statistics on Functions comprising the Dhrystone Benchmark after                                                                            |          |

| 6.2                               | One Hundred and One Million Passes                                                                                                                | 63       |

| <ul><li>6.2</li><li>6.3</li></ul> | Dhrystone SnoopP Counter Assignments                                                                                                              | 65       |

| 0.5                               | 400 Different Keys with 10 Thousand Blocks Each                                                                                                   | 71       |

| 6.4                               | AES SnoopP Counter Assignments                                                                                                                    | 72       |

|                                   | •                                                                                                                                                 |          |

| 7.1<br>7.2                        | Example output equations for the systems in Figure 7.2                                                                                            | 78       |

| 7.3                               | clock cycles                                                                                                                                      | 82       |

|                                   | clock cycles                                                                                                                                      | 84       |

| D.1                               | mb-gprof Statistics on Functions comprising the Dhrystone Benchmark after One Hundred and One Million Passes.                                     | 182      |

| D.2                               | Cycle-Accurate Results using SnoopP to Profile Dhrystone on MicroBlaze systems that include and exclude the Hardware Multiplier and Divider       | 183      |

| D.3                               | The Results from Profiling AES on-chip with SnoopP for Both 2 and 400                                                                             | _ 00     |

|                                   | Keys.                                                                                                                                             | 183      |

| D.4                               | mb-gprof Statistics on Functions Comprising the AES Benchmark for 2                                                                               |          |

|                                   | and 400 Different Keys with 10 Thousand Blocks Each                                                                                               | 184      |

## Glossary

API Application Programming Interface

ASIC Application Specific Integrated Circuit

BRAM Block RAM

CAD Computer Aided Design

CE Computing Element

CLB Configurable Logic Block

EX IR Executing Instruction Register

FPGA Field Programmable Gate Arrays

FSL Fast Simplex Links FSM Finite State Machine

HDL Hardware Description Language

IC Integrated Circuit

IDCT CE Inverse Discrete Cosine Transform CE

IP Intellectual Property

IQ CE Inverse Quantizer

ISS Instruction Set Simulator

LSB Least Significant Bits

LUTs Look Up Tables

MC/PR CE Motion Control/Picture Reconstruction CE

MDM Microprocessor Debug Module

MHS Microprocessor Hardware Specification

MMR CE Missing Macroblock Replacer CE

MPD Microprocessor Peripheral Definition

MSS Microprocessor Software Specification

NoC Network-on-Chip

OCP Open Core Protocol

OPB On-chip Peripheral Bus

PAO Peripheral Analyze Order

PC Program Counter

PCB Printed Circuit Board

PE Processing Element

SCS SIMPPL Control Sequencer

SIMPPL Systems Integrating Modules with Predefined Physical Links

SnoopP Snooping Profiler

SoC System on Chip

SUT System Under Test

VLD/RLD CE Variable Length Decoder/Run Level Decoder CE

VSIA Virtual Socket Interface Alliance

WOoDSTOCK Watching Over Data STreaming On Computing element linKs

XMP Xilinx Microprocessor Project

XPS Xilinx Platform Studio

# Chapter 1

### Introduction

Historically designers created computing systems by combining Integrated Circuits (ICs) on Printed Circuit Boards (PCBs). However, due to the decreasing size of process technologies, designers have been able to implement these same systems as Systems-on-Chip (SoCs) using Application Specific Integrated Circuits (ASICs) since the late 1990's. The term System-on-Chip (SoC) has been used with many different connotations in previous work. For this study, we define an SoC as a collection of functional units on one chip that interact to perform a desired operation. These modules are typically of a coarse granularity so that previously designed Intellectual Property (IP) modules can be reused to try and reduce the design time of more complex systems. Examples of IP modules range from data intensive processing cores, such as FIR filters and FFTs, to more control intensive cores, such as memory controllers and processors.

#### 1.1 Motivation

IP reuse is more challenging in hardware designs than reusing software functions in new software applications. Software designers benefit from a fixed implementation platform with a highly abstracted programming interface, enabling them to focus on adapting the functionality to the new application. Unfortunately, to reuse hardware IP [1, 2], designers need to consider changes to the module's:

- functionality,

- physical interface, and

- communication protocols.

Depending on the amount of time required to adapt IP to a new application, there may be little benefit in reusing the IP to create new SoCs. However, if we create a framework for describing SoCs to simplify the integration of IP modules, it would allow hardware designers to focus on adapting IP functionality similar to software designers updating software functions.

Another challenge for SoC designers is verifying design functionality and performance in a timely fashion. Designers have traditionally relied on simulation and estimation to evaluate their systems. Given the potential size and complexity of SoCs, simulation can be a very time consuming process that takes orders of magnitude longer than on-chip execution. However, if an SoC is implemented on an ASIC, it has a restrictive design environment that is not easily altered post fabrication. Therefore, the importance of correctly implementing a design on an ASIC the first time necessitates lengthy simulation times to prevent a costly redesign.

Now that commercial Field Programmable Gate Arrays (FPGAs) are also large enough to implement entire systems on one chip [3, 4], as opposed to just the glue logic, they offer a unique opportunity for SoC designers. When using a reconfigurable implementation platform, there is no cost to reprogramming the hardware, therefore, we can develop a new design infrastructure where system evaluation is performed on-chip. It would provide greater flexibility to the designer and allow a new approach to the design process. For example, Hemmert et al. [5] introduced a debugger for hardware designs capable of running on an FPGA for the benefit of accelerated speed of execution during the debugging process. Recent work allows designers to incorporate a *Statistics Module* into a soft processor to obtain a variety of run-time statistics that can be dynamically reconfigured [6]. Furthermore, designing for a reconfigurable implementation platform enables designers to easily respecify the system's architecture if the on-chip evaluation determines that the current architecture fails to meet design specifications.

#### 1.2 Objective

The objective of this research is twofold:

- To study how creating a framework for SoC architectures can facilitate both IP reuse and system design.

- To develop a set of on-chip CAD tools that can exploit FPGAs to reduce time spent evaluating the functionality and performance of SoCs.

Defining a system framework requires that the system-level communication structure used to integrate the IP modules be characterized. It also necessitates the specification of the physical interface as well as the communication protocols for IP modules, to facilitate their reuse in different applications. Finally, a formalized method for adapting how an IP module is used by different systems without necessitating significant redesign is desired to facilitate design reuse.

Having created a system framework, it is possible to develop on-chip CAD tools that can be tailored to different SoC architectures. Given the unrestricted ability to reprogram an FPGA, on-chip CAD tools can be used during the design process to evaluate functionality and performance. By performing these operations on the runtime platform, designers can reduce simulation time and overall design time.

#### 1.3 Contributions

This thesis can be divided into two significant contributions:

- an architectural framework for SoCs, and

- a design infrastructure developed to leverage the advantages of reconfigurability and a defined SoC model.

The proposed framework models SoCs as Systems Integrating Modules with Predefined Physical Links (SIMPPL [7]) to expedite system integration. Within this framework, IP modules are abstracted as Computing Elements (CEs) to reduce the complexities of adapting IP to new applications. A lightweight controller has been created to provide a fixed system-level interface for the IP module with standardized communication protocols. It also executes a program that dictates how the IP is used in the system, thus localizing the system-level control to simplify any necessary functional redesign of the IP for other applications.

Designers implementing SoCs on FPGAs can leverage configurability by moving the evaluation of the system on-chip. This can reduce system design time by decreasing the amount of time spent simulating the system's runtime behaviour, while still providing accurate information. To this end, two on-chip profiling tools, SnoopP [8] and WOoD-STOCK [7] have been designed. Furthermore, fixing the SoC architectural framework allows us to create a system specification tool [7] that can facilitate the redesign of the system-level architecture and an on-chip verification environment [9] for SoCs implemented on FPGAs using the SIMPPL model.

### 1.4 Thesis Organization

This thesis is divided into eight chapters. Chapter 2 summarizes the previous work done on IP reuse and on-chip communication structures and presents the SIMPPL framework for SoC design. Chapter 3 describes the Computing Element (CE) abstraction that is central to this model. To demonstrate how the SIMPPL framework and CE abstraction can facilitate design, three applications are implemented as SoCs as described in Chapter 4. The remainder of the thesis document discusses designing SoCs on FPGAs. Chapter 5 provides an overview of current research and describes the system-level design tools created for generating and verifying SoCs within the SIMPPL framework on FPGAs. Along with these tools, the design infrastructure for SoCs on FPGAs also includes two profiling tools for evaluating system performance. The first is SnoopP, a *Snoop*ing *P*rofiler for measuring the performance of applications on processors at runtime, which is discussed in Chapter 6, and WOoDSTOCK is the other. Chapter 7 describes how Watching Over Data STreaming On Computing element linKs (WOoDSTOCK) can be used to detect processing load imbalances in systems modelled using SIMPPL. Finally, the conclusions and potential future work for this thesis are summarized in Chapter 8.

# Chapter 2

# **Modelling SoCs: SIMPPL**

This chapter begins by summarizing popular methods of simplifying IP reuse in Section 2.1, followed by a discussion of some of the previous work investigating on-chip interconnect structures in Section 2.2. It concludes with a presentation of the SIMPPL system framework for SoC design in Section 2.3.

#### 2.1 IP Reuse

Multiple books exist discussing the complexities involved in reusing legacy IP in new designs [1, 2]. Although IP reuse can reduce design time, problems that arise when incorporating previously designed modules into new designs are of significant concern. This has led to the development of well-defined IP design methodologies [10, 11] to ensure reusability of cores with fixed interfaces and functionality. It does not, however, address the common situation where a module has defined functionality but requires the ability to interface with different communication structures.

The Spirit Consortium [12] has created two specifications for facilitating IP reuse. The first is the IP meta-data description, which provides a generic method for describing IP modules. The consortium has also created an IP tool integration API that allows designers to integrate tools into an IP framework for SoC design.

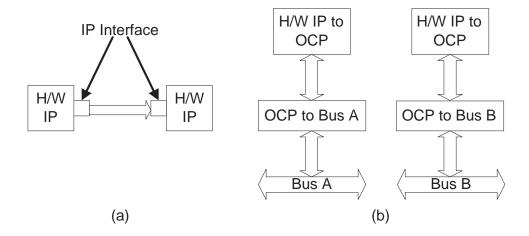

The VSI Alliance has proposed the Open Core Protocol (OCP) [13] to enable the separation of external core communications from the IP core's functionality, similar to the SIMPPL model. Both communication models are illustrated in Figure 2.1. The SIMPPL model targets the direct communication model using a defined, point-to-point interconnect structure for all on-chip communications. In contrast, OCP is used to provide a well-

Figure 2.1: Standardizing the IP interface using (a) SIMPPL for point-to-point communications and (b) OCP for different bus standards.

defined socket interface for IP that allows a designer to attach interface modules that act as adaptors to different bus standards that include point-to-point interconnect structures as shown in Figure 2.1(a). This allows a designer to easily connect a core to all bus types supported by the standard.

More recently, an Interface Adaptor Logic (IAL) layer has been proposed [14] that uses a socket interface for IP modules, similar to the OCP. However, unlike OCP, it is specifically aimed at IP reuse in reconfigurable SoCs. FPGA companies also recognize the importance of simplifying the inclusion of previously designed IP into newer system designs. Xilinx provides its own bus-interface module for interconnecting IP with a defined socket interface [15].

All the protocols presented in this section make it easier to port IP among different bus standards. For example, the OCP and the IAL layer provide standardized adapters that allow cores of fixed functionality to connect to a variety of bus standards. The SIMPPL model, however, has a fixed interface, supporting only point-to-point connections with the objective of allowing is to enable designers to treat IP modules as programmable coarse-grained functional units. Designers can then reprogram the IP module's usage in the system to adapt to the requirements of new applications.

### 2.2 On-Chip Communication Structures

Many different on-chip interconnect strategies have been proposed for SoC design, including hierarchical buses that use bridges to connect to each other [16, 17, 18], but the

maximum bandwidth for each bus is limited by the number of modules connected to it. The WISHBONE [19] SoC interconnect architecture provides multiple different interconnect structures, allowing the designer to select the bus architecture for a particular system. Since all the Wishbone interconnects are designed as single-level buses, the standard provides the user with a simpler design approach, unless components running at different clock rates must share the same bus.

Berkeley's SCORE [20] architecture divides system computations into fixed-size pages and uses the data abstraction of streams to pass data between pages. Streams provide a high-level description of point-to-point communication, comparable to the SIMPPL internal communication link, but without defining a physical connection. Adaptive System-on-chip (aSOC) [21] uses a physical implementation of a point-to-point communication architecture for heterogeneous systems, where unlike the SIMPPL model, the communication interface for each module is tailored in hardware to optimize the module's performance.

Networks provide another form of scalable on-chip communication. Multiple Network-on-Chip (NoC) topologies have been studied for ASIC designs [22, 23]. One popular NoC topology is the mesh [24, 25], which has also been investigated on an FPGA platform [26]. The SIMPPL model, however, can be used to implement any fixed point-to-point network topology, allowing the designer to choose the appropriate topology for each application.

#### 2.3 SIMPPL Model

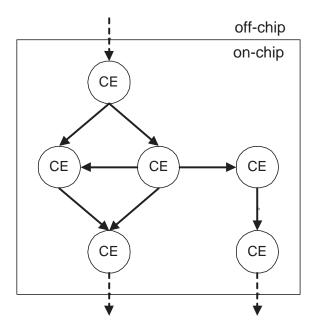

The proposed SIMPPL model represents SoCs as Systems Interfacing Modules with Predefined Physical Links (SIMPPL) [7], implementing an SoC as a combination of different Computing Elements (CEs) that are connected via communication links. Figure 2.2 illustrates a possible SoC architecture described using the SIMPPL model, where the solid lines indicate *internal links* and the dotted lines indicate *I/O communication links*. I/O communication links may require different protocols to interface with off-chip hardware peripherals, but the internal links are standardized physical links with defined communication protocols to make the actual interconnection of CEs a trivial problem and to create a framework for systems design. The current work using the SIMPPL model assumes that the internal links are n-bit wide Asynchronous FIFOs with a user defined depth. Using asynchronous FIFOs simplifies multi-clock domain systems, allowing designers to isolate different clock domains in different CEs and buffer the data transfers between CEs. Point-to-point links not only offer higher bandwidth than shared buses, but recent work has demonstrated that commercial FPGA routing fabrics can implement network topologies where CEs have a high

Figure 2.2: A generic SoC described using the SIMPPL model.

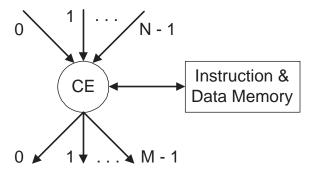

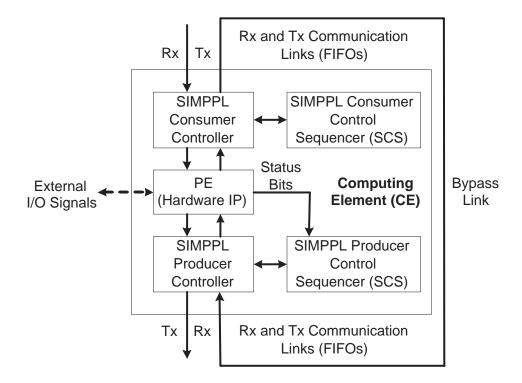

Figure 2.3: The system generator's generic computing element.

degree of connectivity without performance degradation due to routing congestion [27].

Each CE has the generic structure shown in Figure 2.3, where each CE has *N* input links and *M* output links. Internal links connect a CE to other CEs, where input links connect to *parent* CEs and output links connect to *child* CEs. The information passed between CEs is abstracted from the links themselves and instead, the data transfers are adapted to the specific requirements of each CE. This format of communicating data between modules is akin to software design, where the stack provides the physical interface between software functions, similar to the proposed internal links. However, the information passed on the stack, such as the number of parameters, is determined by the individual function calls. In the SIMPPL model, the size and nature of the data in the packet communicated between

the IP modules performs this task. Each module has internal protocols capable of properly creating and interpreting the information in a packet.

A proposed model for the future of SoC design using many interacting heterogeneous processors [28] can also have the same structure as a SIMPPL SoC, however the SIMPPL model is more general, allowing CEs to depict either processors (software CEs) or dedicated logic modules (hardware CEs). The SIMPPL model representation of SoCs is more reminiscent of Kahn process networks [29], particularly Data process networks [30], in that it is a collection of CEs interconnected via unidirectional links and well suited to data intensive applications. However, unlike these models that assume the internal links have unbounded capacity, the SIMPPL model uses real FIFOs that have limited capacity. Work at Philips Research produced YAPI [31], an application model based on Kahn process networks that has been extended to support non-deterministic events and decouple the data types used for communications and computation.

Although the SIMPPL model allows non-deterministic events, they are supported by the CE abstraction. The abstraction allows inter-CE synchronization to be programmed to meet the specific requirements of each application. The SIMPPL model only provides a physical structure for the system and is oblivious to the meaning of the data flowing between CEs, deferring the interpretation of the data to the CE abstraction discussed in the following chapter.

# Chapter 3

# **The Computing Element Abstraction**

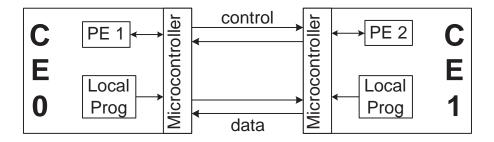

The Computing Element (CE) is an abstraction of software or hardware IP that facilitates design reuse by separating the datapath (computation), the inter-CE communication, and the control. Researchers have demonstrated some of the advantages of isolating independent control units for a shared datapath to support sequential procedural units in hardware [32]. This is similar to when a CE is implemented as software on a processor (software CE), the software is designed with the communication protocols, the control sequence, and the computation as independent functions. Should a software CE need to be reused and updated for a new application, the software changes should be localized to only the control sequence functions.

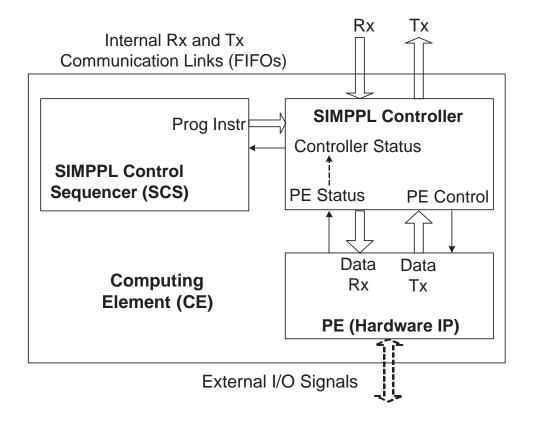

Typically, complex control is easier to implement in software than in hardware. Figure 3.1 illustrates the desired functionality of a hardware CE. Using a microcontroller as the CE communication interface isolates the Processing Element's (PE's) functionality from the rest of the system. The PE now operates as a coarse grain functional unit that is only accessible via the microcontroller. The PE's local control is encapsulated in the CE's local program. Its instructions, along with data requests from adjoining CEs, are interpreted by

Figure 3.1: The concept for the hardware CE.

Figure 3.2: The hardware CE abstraction.

the microcontroller and executed by the PE.

However, general purpose microcontrollers are too big and too slow for the hardware-to-hardware interactions of dedicated logic modules in hardware CEs. Ideally, a controller customized to each CE's datapath could be used as a generic system interface, optimized for that specific CE's datapath. To this end, we've created two versions of a fast, programmable, lightweight controller – an execution-only (*execute*) version and a run-time debugging (*debug*) version – that are both adaptable to different types of computations suitable to SoC designs on both ASICs and FPGAs.

Figure 3.2 illustrates how the control, communications and the datapath are decoupled in hardware CEs. The Processing Element (PE) represents the datapath of the CE or the IP module, where an IP module implements a functional block having data ports and control and status signals. It performs a specific function, be it a computation or communication with an off-chip peripheral, and interacts with the rest of the system via the SIMPPL controller, which interfaces with the internal communication links. The SIMPPL Control Sequencer (SCS) module allows the designer to specify, or "program", how the PE is used in the SoC. It contains the sequence of instructions that are executed by the controller for a

given application. The controller then manipulates the control bits of the PE based on the current instruction being executed by the controller and the status bits provided by the PE. Section 3.3.2 illustrates a programming example for the SCS.

The remainder of this chapter is divided into the following sections. Section 3.1 provides details on the underlying SIMPPL controller architecture and Section 3.2 outlines the additional functionality and hardware of the "debug" version of the controllers. Finally, the SIMPPL Controller Sequencer's interface and programming model are discussed in Section 3.3.

#### 3.1 SIMPPL Controller

The SIMPPL controller acts as the physical interface of the IP core to the rest of the system. Its instruction set is designed to facilitate controlling the core's operations and reprogramming the core's use for different applications. Details on the controller's architecture and the instructions it supports are given below.

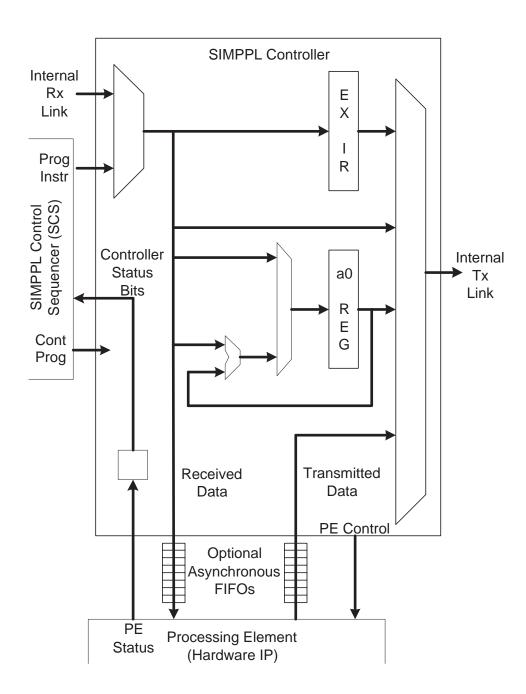

#### 3.1.1 Controller Architecture

Figure 3.3 illustrates the SIMPPL controller's datapath architecture. The controller executes instructions received via both the internal receive (Rx) link and the SCS. Instructions from the Rx Link are sent by other CEs as a way to communicate control or status information from one CE to another CE, whereas instructions from the SCS implement local control. Instruction execution priority is determined by the value of the Cont Prog bit so that designers can vary priority of program instructions depending on how a CE is used in an application. If this status bit is high, then the "program" (SCS) instructions have the highest priority, otherwise the Rx link instructions have the highest priority. Since the user must be able to properly order the arrival of instructions to the controller from two sources, allowing multiple instructions in the execution pipeline greatly complicates the synchronization required to ensure that the correct execution order is achieved. Therefore, the SIMPPL controller is designed as a single-issue architecture, where only one instruction is in flight at a time, to reduce design complexity and to simplify program writing for the user. The SIMPPL controller also monitors the PE-specific status bits that are used to generate status bits for the SCS, which are used to determine the control flow of a program as discussed in Section 3.3.1.

The format of an output data packet sent via the internal transmit (Tx) link is dictated

Figure 3.3: An overview of the SIMPPL controller datapath architecture.

by the instruction currently being executed. The inputs multiplexed to the Tx link are the Executing Instruction Register (EX IR), an immediate address that is required in some instructions, the address stored in the address register  $a\theta$  and any data that the hardware IP transmits. Data can only be received and transmitted via the internal links and cannot originate from the SCS. Furthermore, the controller can only send and receive discrete packets of data, which may not be sufficient for certain types of PEs requiring continuous data streaming. To solve this problem, the controller supports the use of optional asynchronous FIFOs to buffer the data transmissions between the controller and the PE. The designer can then clock the controller at a faster rate than the PE to guarantee that it accurately receives/transmits at the necessary data rate.

#### 3.1.2 Controller Instruction Set

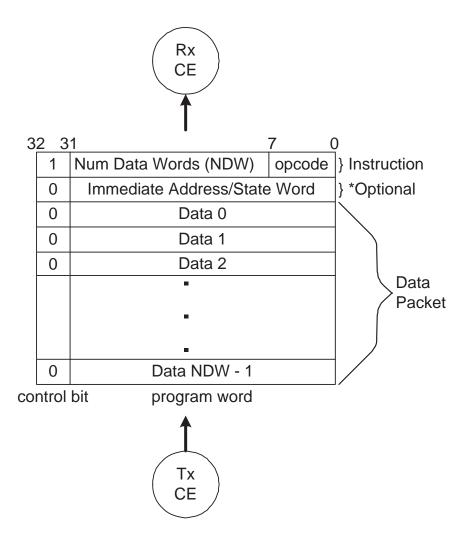

Although the current SIMPPL controller uses a 33-bit wide FIFO, the data word is only 32-bits. The remaining bit is used to indicate whether the transmitted word is an instruction or data. Figure 3.4 provides a description of the generic data packet structure transmitted over an internal link. The instruction word is divided into the least significant byte, which is designated for the opcode, and the upper 3 bytes, which represents the Number of Data Words (NDW) sent or received in a data transmission instruction. The current instruction set uses only the five Least Significant Bits (LSBs) of the opcode byte to represent the instruction. The remaining bits are reserved for future extensions of the controller instruction set.

Designers can choose to reduce the resource usage of SoCs using the SIMPPL model that do not require a 32-bit data word length or address space. If the width of the data word transmitted/received by a CE is less than 32-bits and the maximum number of data words, the NDW value, is less than 2<sup>23</sup>, then the designer may choose to reduce the width of the FIFOs used as internal Rx and Tx links for that CE. For example, if the width of the data words being processed by a CE is 24-bits, the internal links can be 25-bits wide, where 24-bits are used for the data word and one bit is used as the control bit. The opcode of the instruction word would still be the eight LSBs, however, there would only be two bytes to represent the NDW value for the instruction, decreasing the packet size that could be received or transmitted by the CE.

All SIMPPL controller instruction packets have three components: (1) the instruction word; (2) the address or state word (optional); and (3) the data words (optional). The instruction set is divided into two groups; instructions that perform a control operation, and

Figure 3.4: An internal link's data packet format.

those that transfer data. Instructions resulting in data transfers are further subdivided into three different categories: (1) read requests, (2) receives, and (3) writes. A read request is issued by the program of one CE and sent to another CE requesting that data be transmitted back to the original CE. A receive instruction must then be generated as the first transmitted word to accompany the data sent back to the initiating CE, since all transfers via internal links start with an instruction. Finally, the program can also use a write instruction to accompany data words transmitted to another CE.

Table 3.1 contains all the instructions currently supported by the SIMPPL controller and Appendix A.1 lists the instructions and their corresponding opcodes. The objective is to provide a minimal instruction set to reduce the size of the controller, while still providing sufficient programmability such that the cores can be easily reconfigured for any potential application. Although some instructions required to fully support the reconfigurability of

| Instruction Type          | Rd  | Rx | Wr | Issue | Exec. | Addr  | Data  |

|---------------------------|-----|----|----|-------|-------|-------|-------|

|                           | Req |    |    | Instr | Instr | Field | Field |

| Imm. Data Transfer        | X   | X  | X  | S/R   | S/R   |       | X     |

| Imm. Data + Imm. Addr.    | X   | X  | X  | S/R   | S/R   | X     | X     |

| Addr. Reg. Initialization |     |    | X  | S     | S     | X     |       |

| Addr. Reg. Arithmetic     |     |    | X  | S     | S     |       |       |

| Imm. Data + Indir. Addr.  | X   | X  | X  | S     | S     | X     | X     |

| Imm. Data + Autoinc.      | X   | X  | X  | S     | S     | X     | X     |

| Bypass                    |     |    |    | S/R   | S/R   |       | X     |

| No-op                     |     |    |    | S     | R     |       |       |

| Reset                     |     |    |    | S     | R     |       |       |

Table 3.1: The current instruction set supported by the SIMPPL controller.

some types of hardware PEs may be missing, the instructions in Table 3.1 support the hardware CEs that have been built to date. Furthermore, the controller supports the expansion of the instruction set to meet future requirements.

The first column in Table 3.1 describes the operation being performed by the instruction. Columns 2 through 4 are used to indicate whether the different instruction types can be used to *request data* (Rd Req), *receive data* (Rx), or *write data* (Wr). The next two columns are used to denote whether each instruction may be issued from or executed from the *SCS* (S) or *internal Receive Communication Link* (R). Finally, the last two columns are used to denote whether the instruction requires an *address field* (Addr Field) or a *data field* (Data Field) in the packet transmission.

The first instruction type described in Table 3.1 is the immediate data transfer instruction. It consists of one instruction word of the format shown in Figure 3.4, excluding the address field, where the two LSBs of the opcode indicates whether the data transfer is a read request, a write, or a receive. The immediate data plus immediate address instruction is similar to the immediate data transfer instruction except that an address field is required as part of the instruction packet.

Instructions that use the *a0* register have a one or two-word format, but are not transmitted as they only make sense in the context of the local controller. The initialization of the local address register with an immediate value is a two word instruction, where the first contains the opcode and the second is the new address. The address register arithmetic

Figure 3.5: A Data packet with four bypass instructions.

instructions are single word instructions used to add or subtract an offset to the current local address register value. The value in the address register can provide the immediate address for any data transfer instructions sent to other CEs, using indirect addressing with an optional post-increment.

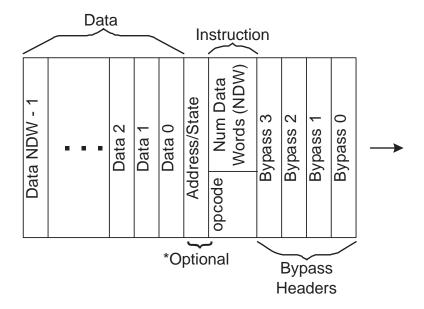

The remaining instructions provide control functionality for the controller. The *bypass* instruction allows a packet of data received from one CE to bypass the current CE, such that the bypass instruction header is removed and the enclosed instruction is forwarded without execution. Figure 3.5 illustrates a data packet that is encompassed within four bypass instructions. By prepending N bypass instructions to a data packet, the packet will bypass N controllers before the  $N+I^{th}$  controller processes the actual data packet. The *no-op* instruction can be used in combination with SCS status bits to provide handshaking controls between CEs. This will be further discussed in Section 3.3.1. Finally, the *reset* instruction can be transmitted from the CE to reset the controller and PE of the receiving CE.

Designers can reduce the size of the controller by tailoring the instruction set to the PE. Although some CE's may receive and transmit data, thus requiring the full instruction set, others may only produce data or consume data. The Producer controller (Producer) is designed for CE's that only generate data. It does not support any instructions that may read data from a CE. The Consumer controller (Consumer) is designed for CEs that receive input data without generating output data. It does not support any instructions that try to

Figure 3.6: The SIMPPL debug controller architecture.

write PE data to a Tx link.

### 3.2 Debug Controllers

Here we introduce a debug SIMPPL controller (debug controller), based on the execute SIMPPL controller (execute controller) described in Section 3.1. This extension of the original architecture allows designers to detect low-level programming and integration errors for individual CEs.

#### 3.2.1 Debug-Controller Architecture and Interface

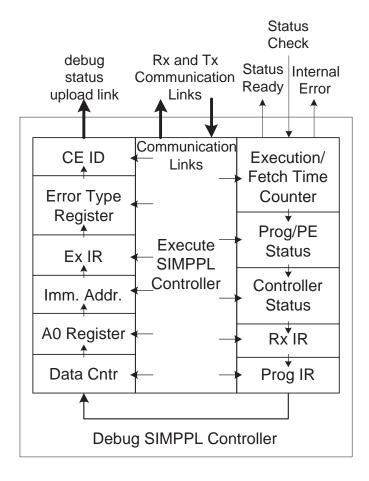

Figure 3.6 shows the architecture of a debug controller, with the execute controller described in Section 3.1 forming the central component. While the execute controller has three states in the instruction execution state machine: fetch, decode, and execute, the de-

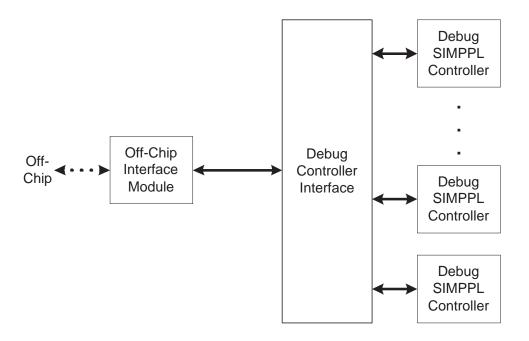

Figure 3.7: The SIMPPL debug controller interface.

bug controller has a fourth state – the *stall* state. An input signal (Status Check) has been added to the debug controller to allow designers to request a status check of the CE while the system is running. Additional output signals are used to indicate if a run-time error has occurred in the CE(*int\_error*) and when the CE's status information is ready to be accessed (*status\_ready*). The controller enters the stall state if an error occurs during the execution of an instruction or if a status check has been requested (*status\_check*). The stall state allows the controller to upload all of the status information about the current executing instruction to the debug status upload link before executing the next instruction.

Eleven status registers have been added to the debug controller architecture, as shown in Figure 3.6, to store run-time status information about the CE. These include the CE's ID register, registers that store information about the instruction currently executing (Ex IR, Imm Addr, A0 register, Data Cntr, Execution/Fetch Time Counter), the current state of the CE (Error Type Register, Prog/PE Status, Controller Status), and the "next" instructions available from the program and from the receive link (Rx IR and Prog IR). The status registers are connected to form a large shift register to upload the values from the CE to the debug status upload link. The debug controller requires twelve cycles, or one cycle plus the number of status registers, in the stall state to upload all of the status information from the CE to the link, assuming the upload link is not full. Otherwise, the controller will remain in the stall state until all the status register values have been uploaded.

The debug status upload link is implemented as an additional Asynchronous FIFO link

Table 3.2: The current error cases detectable using the debug controller.

| Error Case                                        | Error Code | Error Type  |

|---------------------------------------------------|------------|-------------|

| Instruction word not in Fetch Cycle               | 8000 0001  | Programming |

| Data word in Fetch Cycle                          | 4000 0001  | Programming |

| Execution Time Overflow                           | 2000 0001  | Programming |

| Fetch Time Overflow                               | 1000 0001  | Programming |

| Writing to a Full Tx Link                         | 0800 0001  | Integration |

| Reading from an Empty Rx Link                     | 0400 0001  | Integration |

| Writing data to the PE when it is not ready       | 0200 0001  | Integration |

| Writing an address to the PE when it is not ready | 0100 0001  | Integration |

| Reading data from the PE when it is not ready     | 0080 0001  | Integration |

| Executing an invalid instruction                  | 0040 0001  | Programming |

that is used to upload the debugging information to the debug interface shown in Figure 3.7. The debug controller interface connects via a bus to an off-chip peripheral interface module that allows users to read the available status information off-chip from the controllers. The interface also contains a status register that indicates which CEs have status information available and what, if any, CEs have encountered run-time errors. Alternatively, if a debug controller is implemented in ASIC technology, the status information can be downloaded off-chip by implementing the registers using scannable flipflops.

#### 3.2.2 Debugger Options and Detectable Errors

The debug controller supports two different run-time operations: error detection and status checks. When the *Status check* signal is set high for a clock cycle, it triggers the CE to upload status information after the execution of the current instruction completes. This allows the designer to check what instruction is being executed by a CE at random points of operation of the application. The *Status Check* can also be tied high for the duration of the profile period to obtain a continuously running profile of the CE, however, the CE will stall if the upload link becomes full.

Column 1 of Table 3.2 lists the error cases that the debug controller is currently able to detect, but the number of detectable error cases may be extended if a future need is determined. The second column in the table indicates the error code that is uploaded from

the debug controller when an error occurs. The final column indicates whether an error case is the result of a programming error or a CE/system integration error.

# 3.3 SIMPPL Control Sequencer

The SIMPPL Control Sequencer provides the local program that specifies how the PE is to be used by the system. For example, a CE that has an audio sampling PE can be reprogrammed to generate packets of different formats depending on the requirements of the application. In this section, we discuss the SCS's architecture for both ASIC and FPGA platforms and provide a programming example. We then conclude with a discussion of how the CE abstraction allows a designer to dynamically generate program instructions, which we refer to as dynamic programming.

#### 3.3.1 SCS Interface

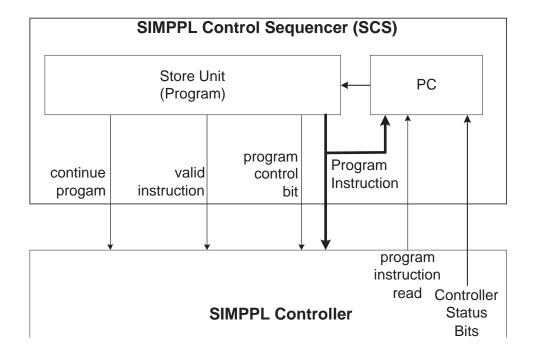

The operation of a SIMPPL controller is analogous to a generic processor, where the controller's instruction set is akin to assembly language. For a processor, programs consist of a series of instructions used to perform the designed operations. Execution order is dictated by the processor's Program Counter (PC), which specifies the address of the next instruction of the program to be fetched from memory. While a SIMPPL controller and program perform the equivalent operations to a program running on a generic processor, the controller uses a remote PC in the SCS to select the next instruction to be fetched.

Figure 3.8 illustrates the SCS structure and its interface with the SIMPPL controller via six standardized signals. The 32-bit *program word* and the *program control bit*, which indicates if the program word is an instruction or address, are only valid when the *valid instruction* bit is high. The *valid instruction* signal is used by the SIMPPL controller in combination with the *program instruction read* to fetch an instruction from the Store Unit and update the PC. The *continue program* bit indicates whether the current program instruction has higher priority than the instructions received on the CE Rx link. It can be used in combination with PE-specific and controller *status bits* to help ensure the correct execution order of instructions.

For example, if the SCS has a status bit that indicates when the controller is executing an instruction from a Rx Link (*exec\_rx\_instr*), it can be used to stall the CE until it has received a packet from an adjacent CE. To perform this handshaking, the SCS program initially stalls the controller by setting the *valid instruction* bit low. When the controller

Figure 3.8: The standard SIMPPL control sequencer structure and interface to the SIMPPL controller.

receives an instruction on the Rx Link, it acts as a request signal and the *exec\_rx\_instr* will go high. In response to this request, the SCS's *valid instruction* signal then goes high along with the *continue program* so that the next instruction executed by the controller is an SCS instruction to acknowledge the received request.

Although a PC is traditionally implemented as a counter, the SCS's remote PC can also be constructed as a Finite State Machine (FSM). This allows branches to be executed implicitly as transitions in the PC's FSM depending on the control and status signal values. The PC FSM is application-specific and uses the current PC and status bit values to generate the correct index to the store unit to select the correct instruction to be fetched and sent to the controller. This reduces the size of both the SIMPPL controller and the program located in the store unit by eliminating the need for branch instructions in the instruction set. Furthermore, it reduces the performance overhead of using the SIMPPL controller as an interface since it does not have to execute conditional or explicit branch instructions.

If an SoC is implemented on an FPGA, the designer can choose to implement the program's store unit in an on-chip memory. Yet many CEs only require small SCSs for an application, thus the instructions can be stored as a separate FSM. When an SoC is implemented as an ASIC, the designer could choose to design each SCS for its specific application by instantiating a small memory for the Store Unit and then implementing

```

write start addr to a0;

for (i=0; i< 1024; i++)

{

while (!valid_sensor_data);

write 8 data words starting at addr (a0);

a0 = a0 + 8;

}</pre>

```

Figure 3.9: Pseudocode for the sensor unit's SCS program.

the PC as application-specific dedicated logic. However, one of the benefits of the CE abstraction is that it decouples the control from the datapath to support programmability. Hardwiring the PC means that the designer cannot alter the CE's program post-fabrication. To allow post-fabrication programmability, ASIC designers can implement a small memory for the instruction words and a small region of programmable fabric that enables designers to change the PC to support a variety of SCS programs for the CE. The following example demonstrates how to write a program and use the SIMPPL controller interface.

### 3.3.2 Static Programming Example

Assume a hardware system that consists of two PEs: 1) a memory, and 2) a sensor unit used to measure multiple environmental quantities at set time intervals. The total storage requirements for each set of measurements is 32 bytes (eight data words) and the memory is large enough to store 1024 samples. The user wants to store the first 1024 samples to experimentally measure when the environmental system reaches steady state before deciding how often to record samples and upload the results to a host PC. The sensor unit has a status bit, *valid\_sensor\_data*, that indicates when a set of measurements is available for reading. The sensor unit's SIMPPL controller passes the status information to its SCS to indicate that data is available for transmission to the memory unit. The pseudocode for the sensor unit's SCS program is given in Figure 3.9. At present, we do not have compiler support for the SIMPPL controller and all programs (SCSs) are hand generated. Figure 3.10 illustrates pseudo-HDL implementations of the sensor CE's Program Counter FSM and the *valid\_instruction* signal that dictate the program instruction and if it is available to be fetched by the SIMPPL controller using the *prog\_instr\_read* signal.

The PC requires four states to implement the pseudocode in Figure 3.9 and the PC state only changes after an instruction has been read or all 1024 samples have been written to memory. The first two states, *Write a0* state and *Write address* state, write the starting

```

if (rst=1) {

PCstate <= Write a0 state;

else

PCstate <= nextPC;</pre>

//Next-state state machine for the PC:

case (PCstate) {

Write a0 state: //Instruction to initialize a0

if ((prog_instr_read) && (rst=0))

nextPC = Write address state;

else

nextPC = Write a0 state;

Write address state: //New address for a0

if (proq instr read)

nextPC = Write autoinc state;

else

nextPC = Write address state;

Write autoinc state: //Write data to (a0)+

if ((prog_instr_read) && (SampleCntr=1024))

nextPC = Done state;

else

nextPC = Write autoinc state;

Done state:

nextPC = Done state;

/*Used to indicate when the instruction is valid.

*Stalls the processor when there is no valid

*instruction. */

case (PCstate) {

Write a0 state:

valid instruction = 1;

Write address state:

valid instruction = 1;

Write autoinc state:

valid instruction = valid sensor data;

Done state:

valid instruction = 0;

```

Figure 3.10: Pseudo-HDL code to implement the state machine for the sensor unit's program counter and the valid instruction signal.

Figure 3.11: A CE with multiple packets of data in flight.

address of the memory unit to the a0 register. The third state (Write autoinc state) writes eight data words to the memory unit starting at address (a0) and then post-increments a0 by eight. While the valid instruction signal is high during the first two states to initialize the address register, it is assigned the value of the valid\_sensor\_data status bit in the Write autoinc state because the data write instruction should only occur when the sensor has new data to transmit to the memory. A separate counter state machine(SampleCntr), not shown in Figure 3.10, is used to count the number of times the sensor unit measurements are sent to the memory unit. When the SampleCntr equals 1024, the program has completed so the PC goes to the Done state, where no further instructions are executed, and the valid\_instruction signal goes low permanently.

### 3.3.3 Dynamic Programming Architecture

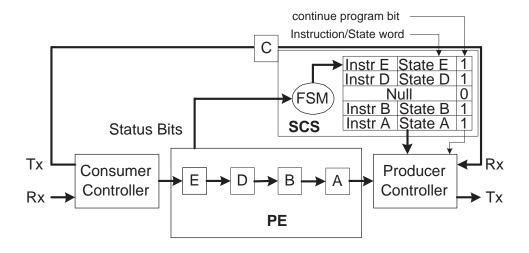

For some applications, a designer may wish to have a CE support multiple processing operations that are data packet dependent. If the CE is pipelined with independent Producer and Consumer controllers for the PE, then the Consumer may receive a variety of instruction packets that should result in the Producer generating different instruction packets depending on the received data. The following example demonstrates how the Consumer and Producer controllers can work together to correctly process the received instruction packets and generate the appropriate output instruction packets, even in the presence of bypass instructions.

Figure 3.11 illustrates a CE that receives packets A through E in order, where packet C is to bypass the PE entirely, and generates the appropriate program instructions for the